¿Tu último diseño de PCB falló por sobrecalentamiento? ¿Has malgastado $3,000 en placas de 12 capas innecesarias? He visto que el 63% de los equipos de hardware cometen errores críticos de apilamiento antes de probar los prototipos. Arreglémoslo.

El apilamiento óptimo de PCB (https://www.ipc.org/system/files/technical_resource/E8%26S22_03.pdf)[^1] utiliza materiales híbridos para las capas críticas, ajusta el número de capas (https://www.ipc.org/system/files/technical_resource/E8%26S15_02.pdf)[^2] a la complejidad de la señal y aplica diseños simétricos para evitar deformaciones. Mi equipo logra una reducción de costos del 25% mediante sustituciones de sustrato[^3] sin sacrificar el control de impedancia.

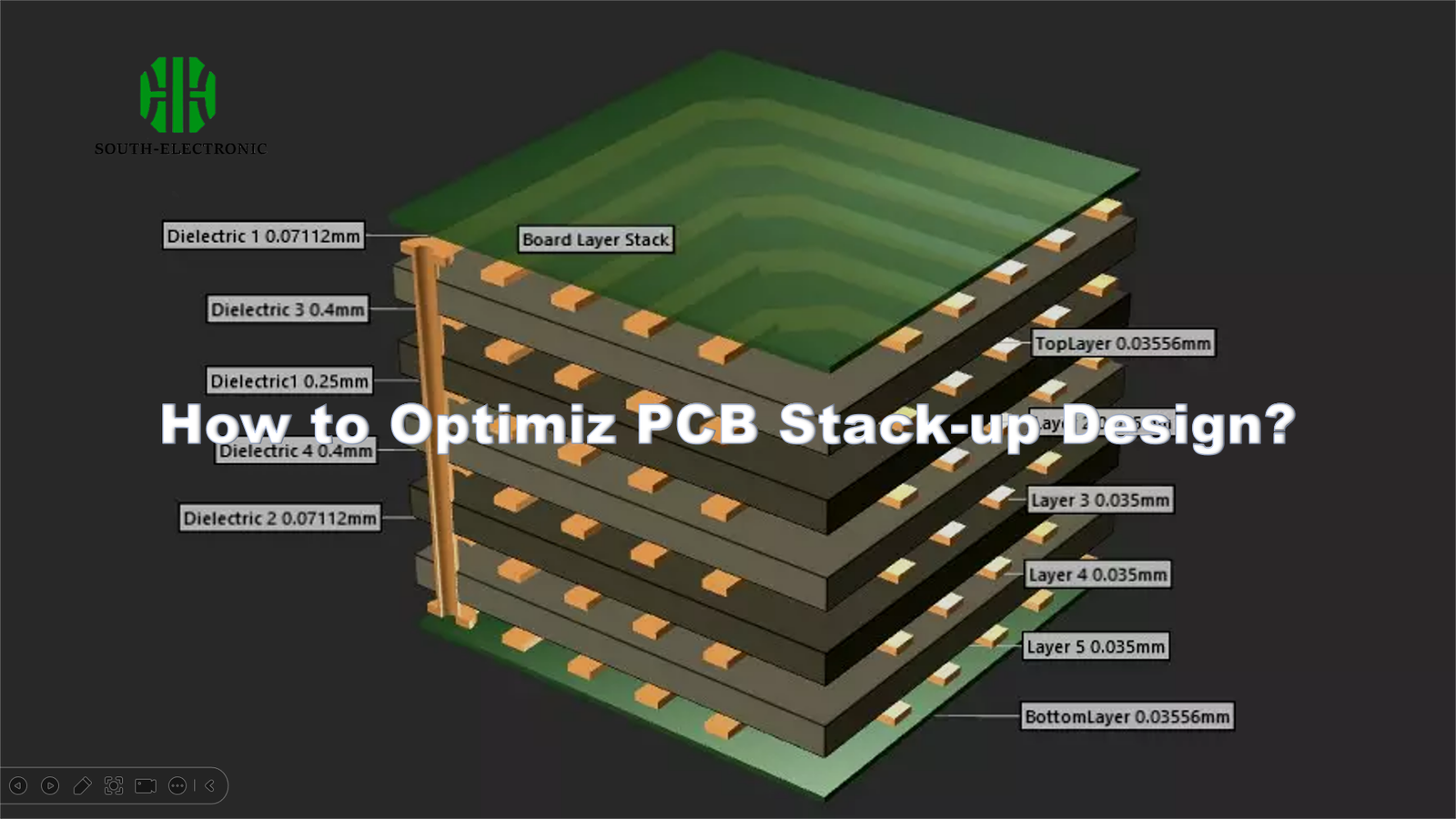

Estas cinco estrategias de apilamiento conforman un marco paso a paso. Desde la planificación del número de capas hasta las soluciones EMI, cada decisión impacta por igual los costos de producción y la confiabilidad de la señal.

¿Cómo determinar el número adecuado de capas para el apilamiento de PCB?

Una placa de 6 capas costó $180 el trimestre pasado. Nuestro nuevo diseño de 4 capas con enrutamiento optimizado cumple la misma función por $112. ¿Cuándo se NECESITAN capas adicionales?

El número de capas depende del tipo de señal: utilice 4 capas para señales de extremo único por debajo de 2 GHz. Se requieren más de 6 capas al combinar circuitos de RF, digitales y de potencia, o al utilizar ≥3 pares diferenciales que requieren aislamiento.

)

Tres determinantes clave para la optimización de capas

| Factor | Casos adecuados de 4 capas | Casos requeridos de 6 capas |

|---|---|---|

| Tipos de señal | DC/1 GHz digital de un solo extremo | RF+digital+analógica mixta |

| Tamaño de la placa | ≥70 mm x 90 mm | <50 mm x 50 mm (se requiere HDI) |

| Limitaciones presupuestarias | Costo del prototipo <200 $/unidad | Optimización de la lista de materiales del producto final |

Prototipo con FR-4 en 4 capas y luego verifico mediante TDR si las discrepancias de impedancia requieren una actualización de capa. El diseño anterior de la fuente de alimentación demostró que 8 capas eran innecesarias: el cambio a cobre de 2 oz en las capas internas ahorró un 18 % en costos de material.

¿Cómo elegir materiales de núcleo para diseño de PCB de alta frecuencia y ordinario?

RO4350B cuesta 7 veces más que el FR-4 estándar. Sin embargo, al usarlo solo en capas críticas de radar de 24 GHz, las pérdidas del sistema se redujeron un 41 %, manteniendo el 84 % de los costos de material sin cambios.

El apilamiento híbrido[^4] funciona mejor: use materiales de alta frecuencia Rogers/Isola solo en capas de radiofrecuencia (≤4). Mantenga las demás capas como FR-4. Asegúrese de que el desajuste del CTE sea <3 ppm/°C entre dieléctricos adyacentes para evitar la delaminación.

)

Criterios de selección de materiales[^5] Tabla

| Aplicación | Material recomendado | Dk a 10 GHz | Tangente de pérdida | Coste por m² |

|---|---|---|---|---|

| Antena de ondas milimétricas 5G | Rogers RO4835 | 3,48 | 0,0037 | $380 |

| Bus de memoria DDR4 | Isola I-Speed | 3,87 | 0,007 | $270 |

| Plano de alimentación de 12 V | Shengyi S1000-2 | 4.3 | 0.02 | $42 |

Combinamos simulación electromagnética y lotes de prueba: Primero, modelamos con materiales ideales y luego reducimos las capas no críticas hasta que la integridad de la señal alcance el límite de tolerancia del 15 %. Este enfoque redujo el gasto de material en un 31 % en el último proyecto WiFi 6E.

¿Qué parámetros clave se requieren para el control de impedancia[^6] de una PCB multicapa?

Una discrepancia de 92 Ω arruinó nuestra ejecución del prototipo. Ahora implemento: variación del peso del cobre ≤0.2 oz, tolerancia del espesor dieléctrico ±8 %, variación de Dk ±0.15.

Parámetros críticos: 1) Espesor del núcleo/revestimiento 2) Factor de compensación de grabado 3) Consistencia Dk/Df en los paneles 4) Uniformidad del recubrimiento. Mantener una desviación de impedancia ≤5 % mediante cortes transversales y comprobaciones puntuales de TDR.

Protocolo de gestión de impedancia

| Parámetro | Método de medición | Rango aceptable | Método de ajuste |

|---|---|---|---|

| Espesor dieléctrico[^7] | Microscopía de corte transversal | ±8 % del valor nominal | Ajuste de preimpregnado laminado |

| Rugosidad del cobre | Perfilómetro | Rz ≤5 μm | Electropulido |

| Consistencia Dk | Prueba de línea de banda sujeta | ±0.15 en lote | Auditoría de proveedores de materiales |

Colaboro con los fabricantes desde el principio, proporcionando objetivos de impedancia específicos para cada capa en lugar de especificaciones generales. Para pares diferenciales de 100 Ω en las capas 3-4: Especifique el espesor dieléctrico exacto (0,204 mm ± 0,015 mm) y utilice cálculos inversos para obtener pesos de cobre y factores de grabado aceptables.

¿Cómo reducir el coste total mediante la optimización de la estructura de apilamiento?

Reducir de 14 a 10 capas redujo drásticamente los costes de producción en un 37 %, pero solo después de demostrar mediante simulación térmica que los apilamientos simétricos previenen la deformación en hornos de refusión.

Tres soluciones para reducir costos:

1) Distribución simétrica del cobre[^8]

2) Reemplazar las vías enterradas por microvías escalonadas[^9]

3) Usar planos de potencia internos de 2oz para eliminar dos capas de señal. Lograr una reducción de costos del 40% manteniendo la funcionalidad de 8 capas.

)

Lista de verificación para la optimización del apilamiento

| Técnica | Impacto en los costos | Dificultad de implementación | Mitigación de riesgos |

|---|---|---|---|

| Fusionar capas de potencia | -15 % por fusión | Medio | Aumentar la distancia entre planos |

| Apilamiento de materiales híbridos[^10] | -22 % de coste de material | Alto | Verificación de coincidencia de CTE |

| Eliminación de vías en almohadillas | -8 % de coste de perforación | Bajo | Redistribuir componentes |

Caso práctico: En un controlador industrial, la transición de un sistema FR4 de 12 capas a un híbrido de 8 capas (Rogers + IT-180A) mantuvo el rendimiento térmico. Se logró una utilización del panel del 65 % al 89 % mediante diseños de apilamiento en espejo, logrando una reducción total del coste del 29 %.

¿Cómo evitar la diafonía y la pérdida de señal en el diseño de apilamiento de PCB de alta velocidad?

¿Pérdida excesiva de 3 dB a 28 GHz? Nuestro análisis reveló un espaciado incorrecto de la conexión a tierra (GND). Ahora implemento: enrutamiento ortogonal de las capas de señal adyacentes, islas de potencia en lugar de planos completos cerca de las trazas de RF.

**Evitar la diafonía mediante: 1) Regla de espaciado de 3 W[^11] 2) Capas de GND intercaladas entre señales de alta velocidad 3) Variación del espesor dieléctrico ≤15 %. Para PAM4 de 56 Gbps, implemente una microbanda invertida con preimpregnado Dk 3 m |

| Ruido en modo común | Planos de potencia divididos con costura | Análisis de parámetros S del analizador vectorial de redes (VNA) |

| Resonancia de ramal de vía | Perforación posterior superior a 1,5 veces el diámetro de la vía | TDR con tiempo de subida de 35 ps |

Regla de diseño final: Asignar señales críticas a las capas 2-3 y 6-7 en placas de 8 capas. Esto proporciona planos de tierra adyacentes y evita problemas de absorción de humedad en la capa exterior. Nuestra validación de PCIe Gen5 x16 mostró una mejora de 0,8 dB/pulgada con esta configuración.

Conclusión

Para equilibrar el rendimiento y el coste se requieren materiales híbridos, optimización del número de capas y protocolos de impedancia estrictos. Implemente estas estrategias de apilamiento para reducir los costes de las PCB entre un 25 % y un 40 % sin comprometer la integridad de la señal en diseños de alta frecuencia.

[^1]: Explorar las mejores prácticas para el apilamiento de PCB puede ayudarle a evitar errores costosos y optimizar sus diseños en cuanto a rendimiento y coste.

[^2]: Entender cómo determinar el número correcto de capas puede tener un impacto significativo en el rendimiento y la rentabilidad de su PCB. [^3]: Aprender sobre la sustitución de sustratos puede generar ahorros de costos y un mejor rendimiento en sus diseños de PCB.

[^4]: Explore este enlace para comprender cómo el apilamiento híbrido puede optimizar su diseño de PCB para lograr un mejor rendimiento y una mejor relación calidad-precio.

[^5]: Descubra los criterios esenciales para la selección de materiales y así mejorar el rendimiento y la fiabilidad de su PCB.

[^6]: Aprenda sobre el control de impedancia para garantizar que sus diseños de PCB cumplan con los estándares de rendimiento y evitar costosas discrepancias.

[^7]: Comprender el espesor dieléctrico es crucial para lograr un control preciso de la impedancia en el diseño de PCB, garantizando un rendimiento óptimo.

[^8]: Explorar este tema revela cómo la distribución simétrica del cobre puede reducir significativamente los costos y, al mismo tiempo, mejorar la fiabilidad de la PCB.

[^9]: Aprender sobre las microvías escalonadas puede ayudarle a optimizar el diseño de su PCB para lograr un mejor rendimiento y una mejor relación calidad-precio.

[^10]: Explore cómo los materiales híbridos pueden reducir significativamente los costos y, al mismo tiempo, mantener el rendimiento.