Esta especificación se aplica a los principales tipos de sustratos cerámicos, como la alúmina (Al₂O₃), el nitruro de aluminio (AlN) y el nitruro de silicio (Si₃N₄), y es compatible con procesos como HTCC (cerámica de co-cocción a alta temperatura), LTCC (cerámica de co-cocción a baja temperatura) y el recubrimiento directo de cobre (DPC).

Durante el proceso de diseño, los parámetros deben ajustarse con flexibilidad según los escenarios de aplicación específicos (como módulos de potencia, circuitos de RF y encapsulados de LED). Se recomienda una estrecha colaboración con el proveedor del sustrato para garantizar una integración fluida de las capacidades de diseño y fabricación.

I. Objetivos de Diseño

-

Alta fiabilidad: Garantizar la estabilidad del sustrato en entornos extremos, como alta temperatura, alta frecuencia y alta potencia.

-

Optimización de la gestión térmica: Aprovechar la alta conductividad térmica de los materiales cerámicos para lograr una disipación térmica eficiente.

-

Rendimiento eléctrico: Cumplir con los requisitos de integridad de señal, adaptación de impedancia y bajas pérdidas.

-

Compatibilidad de procesos: El diseño debe cumplir con las limitaciones de los procesos de fabricación de sustratos cerámicos (como la impresión de película gruesa, el procesamiento de película delgada o DPC).

2. Directrices de selección de materiales

2.1 Materiales del sustrato

-

Alúmina (Al₂O₃): Adecuada para aplicaciones de baja a media potencia (conductividad térmica de 24-28 W/m·K).

-

Nitruro de aluminio (AlN): Alta conductividad térmica (170-200 W/m·K), adecuada para módulos de alta potencia y encapsulados LED.

-

Nitruro de silicio (Si₃N₄): Alta resistencia al choque térmico, adecuada para aplicaciones de alta frecuencia y alta temperatura.

2.2 Materiales de la capa de metalización

-

Capa conductora: Plata (Ag), Cobre (Cu), Oro (Au). Considere la adhesión a la cerámica y la compatibilidad del coeficiente de expansión térmica (CTE).

-

Capa dieléctrica: Esmalte de vidrio o lechada cerámica para garantizar el aislamiento y la resistencia a altas temperaturas.

III. Especificaciones de diseño eléctrico

3.1 Diseño de la disposición

-

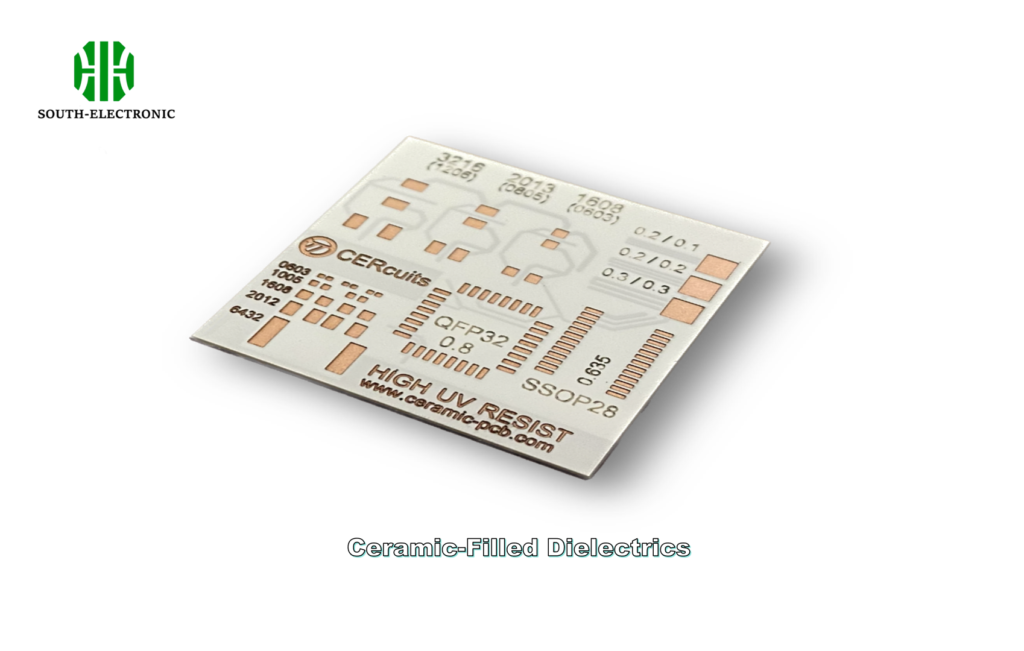

Ancho/Espacio de línea: Ancho mínimo de línea ≥ 50 μm (proceso de película gruesa) o ≥ 20 μm (proceso de película delgada) para evitar el riesgo de cortocircuito.

-

Control de impedancia: La impedancia de la microbanda/línea de banda debe calcularse para señales de alta frecuencia, con un error de ±5 %.

-

Diseño de vías: Diámetro de apertura ≥ 0,1 mm, con metalización uniforme en la pared de la vía (se recomienda perforación láser y relleno de galvanoplastia).

3.2 Conexión a tierra y blindaje

-

Los sustratos cerámicos multicapa requieren una placa de tierra continua para reducir la interferencia electromagnética (EMI).

-

Añada anillos de blindaje o matrices de vías de tierra alrededor de las líneas de señal sensibles.

IV. Especificaciones de diseño para la gestión térmica

4.1 Estructura de disipación térmica

-

Diseñe una amplia área de metalización (como una capa de cobre) debajo del dispositivo de potencia y aumente las vías de disipación térmica.

-

Utilice un diseño de gradiente de conductividad térmica (como un sustrato de AlN con una capa de metalización de cobre).

4.2 Alivio de tensión térmica

- Adaptación del CTE: La diferencia de CTE entre la capa metálica y el sustrato cerámico debe ser ≤ 5 ppm/°C (p. ej., aleación de AlN + cobre tungsteno).

Estructura de transición: Chaflanes en los bordes o enrutamiento escalonado para reducir la tensión mecánica durante los ciclos térmicos.

V. Especificaciones de Diseño Mecánico

5.1 Dimensiones y Tolerancias

-

Rango de Espesor del Sustrato: 0,25 mm a 2,0 mm, con una tolerancia de espesor de ±0,05 mm.

-

Corte: Corte por láser o rayado con diamante, con un desbastado de bordes ≤ 50 μm.

5.2 Almohadillas y Ensamblaje

-

Tamaño de la Almohadilla: Entre un 10 % y un 20 % mayor que el pin del dispositivo para permitir la expansión térmica.

-

Acabado Superficial: Recubrimiento de Oro (ENIG) o Niquelado Químico (apto para soldadura a alta temperatura).

VI. Restricciones del Proceso

6.1 Restricciones de Fabricación

-

Proceso de película gruesa: Ancho mínimo de línea de 50 μm, con resolución limitada por serigrafía.

-

Procesamiento de película delgada: Anchos de línea de hasta 10 μm, que requieren el apoyo de procesos de fotolitografía y pulverización catódica.

-

Procesamiento láser: Precisión de apertura de ±5 μm para evitar grietas en el sustrato causadas por perforaciones repetidas.

6.2 Estándares de Inspección

-

Inspección visual: Sin grietas, delaminación ni desprendimiento de la capa metálica.

-

Pruebas de rendimiento eléctrico: Resistencia de aislamiento ≥ 10¹²Ω, resistencia en estado activo ≤ 50 mΩ.

-

Pruebas de ciclos térmicos: 1000 ciclos de -55 °C a 150 °C sin degradación del rendimiento.

VII. Documentación y Entrega

-

Archivos de salida del diseño: Incluye archivos Gerber, plan de perforación, lista de materiales (BOM) y especificaciones del proceso.

-

Criterios de aceptación: Definir claramente los parámetros eléctricos, las dimensiones mecánicas y los requisitos de las pruebas de fiabilidad.

VIII. Referencia de Escenario de Aplicación Típico

-

Módulo de Potencia: Los módulos IGBT/SiC requieren un sustrato de AlN con metalización de cobre.

-

Dispositivos de RF: Para circuitos de alta frecuencia, se prefieren Al₂O₃ o AlN, que presentan baja pérdida dieléctrica.

-

Encapsulados LED: Los diseños Chip-on-Board (COB) requieren rutas de disipación de calor optimizadas.

IX. Notas

-

Evite las esquinas afiladas: Se recomienda que las esquinas del cableado sean redondeadas o de 45° para reducir la concentración del campo eléctrico.

-

Verificación del Proceso: Los nuevos diseños deben someterse a una producción de prueba en lotes pequeños (p. ej., de 3 a 5 unidades) para confirmar el rendimiento.

Las especificaciones anteriores pueden ajustarse según el tipo de sustrato cerámico específico (p. ej., HTCC, LTCC, DPC) y los requisitos del proyecto. Analice a fondo los detalles del proceso con el proveedor del sustrato antes de diseñar.