Las fallas en las PCB de alta velocidad cuestan a los ingenieros innumerables horas de depuración. Su diseño de vanguardia se derrumba bajo señales de GHz. Arreglemos trazas inestables, caos de EMI y distorsiones de señal a través de optimizaciones de cableado estratégicas.

Optimice el cableado de PCB de alta velocidad priorizando el control de impedancia (tolerancia del 4-6%), minimizando los muñones de via con taladrado inverso y utilizando pares diferenciales simétricos. Implemente pilas de capas con blindaje de tierra y valide los diseños antes de la producción con Ansys SIwave para garantizar la integridad de la señal y el cumplimiento de la EMI.

Estas técnicas separan los prototipos funcionales de los pesos de papel que emiten radio. A continuación, analizaré las estrategias de optimización críticas probadas en más de 12 proyectos de alta velocidad.

¿Entendiendo los desafíos de la integridad de la señal en el cableado de PCB de alta velocidad?

¿Alguna vez ha visto señales que se asemejan a ruido en su osciloscopio? A 5Gbps+, las reflexiones y el acoplamiento corruptan los datos. Descifremos los enemigos invisibles que sabotean sus señales.

Las señales de alta velocidad enfrentan desajustes de impedancia (que causan reflexiones), acoplamiento entre trazas paralelas y pérdidas por efecto de piel. Mitigue estos manteniendo planos de referencia continuos, evitando giros de 90° y manteniendo trazas <1/10 de la longitud de onda de la señal.

Factores críticos que impactan la calidad de la señal

| Desafío | Causa principal | Solución |

|---|---|---|

| Ruido de reflexión | Descontinuidades de impedancia | Ajuste la impedancia de la traza Z0 al controlador/receptor |

| Acoplamiento | Acoplamiento entre trazas | Regla de espaciado de trazas 3X |

| Atenuación | Pérdidas dieléctricas + conductor | Use material Rogers de baja pérdida |

| Salto de tierra | Caminos de retorno inductivos | Planos de tierra sólidos debajo de las trazas |

El efecto de piel aumenta la resistencia a frecuencias de GHz—trazas anchas (8-12 mil) reducen la pérdida. Para pares diferenciales de 100Ω, mantenga un espaciado de 5 mil con un ancho de 6 mil en FR4 (Dk=4.5). Las brechas en el plano de referencia crean picos de impedancia; una vez pasé 3 semanas depurando un diseño de 28GHz solo para encontrar una brecha de 0,5 mm en el plano de tierra.

Reglas de diseño para enrutamiento de impedancia controlada?

Los desajustes de impedancia desencadenan reflexiones de señal. Su enlace de 10Gbps se convierte en un desastre de 1Gbps. Las reglas de enrutamiento de precisión evitan esto.

Calcule el ancho y la altura de la traza usando solvers de campo (por ejemplo, Polar SI9000), mantenga una tolerancia de impedancia de ±5% y evite cambios bruscos de ancho. Enrute sobre planos de referencia continuos con un espaciado dieléctrico controlado para garantizar una impedancia característica consistente a lo largo de todo el camino de la señal.

)

Lista de verificación de control de impedancia

| Parámetro | Impacto en Z0 | Ajuste recomendado |

|---|---|---|

| Aumento del ancho de la traza | Reduce Z0 | Trazas más estrechas |

| Espesor del dieléctrico | Aumenta Z0 | Reduce el espaciado entre capas |

| Valor de Er (Dk) | Un Dk más bajo aumenta Z0 | Cambie a Rogers 4350B |

| Peso del cobre | Un cobre más grueso ↓Z0 | Use cobre de 0,5 oz |

Para líneas estratificadas, Z0 ≈ 87/√(εr+1.41) * ln(5.98h/(0.8w+t)). Enruto trazas individuales de 50Ω con trazas de 8 mil en núcleos de FR4 de 10 mil. Cuando se cruza con divisiones de planos, puente con condensadores de costura (0,1 μF) para mantener los caminos de retorno.

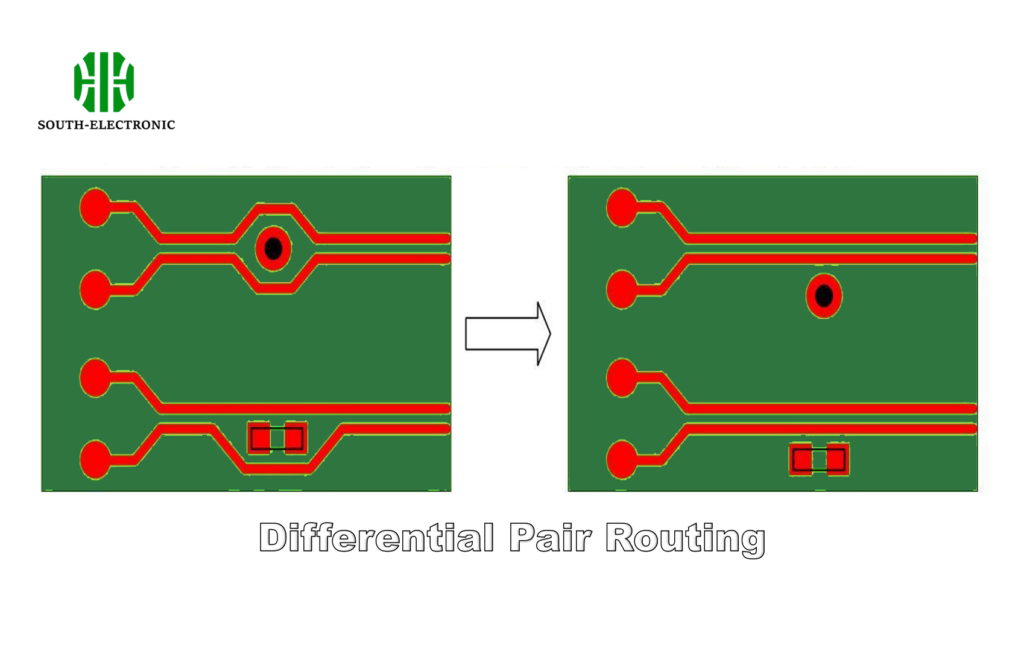

Mejores prácticas para enrutamiento de pares diferenciales?

Pares diferenciales mal emparejados distorsionan las señales. La inestabilidad del reloj se dispara. La simetría es innegociable.

Mantenga un espaciado de par <2X el ancho de la traza, ajuste la longitud de las trazas dentro de 5 mil y enrute simétricamente. Use curvas de ajuste de longitud en los extremos del receptor y minimice las divisiones del plano de referencia debajo de los pares para mantener la rechazada de ruido de modo común.

)

Matriz de optimización de par diferencial

| Parámetro | Práctica deficiente | Práctica óptima | Beneficio |

|---|---|---|---|

| Espaciado | 3X el ancho de la traza | 1X el ancho de la traza | Reduce la EMI en 12dB |

| Coincidencia de longitud | Desajuste de 50 mil | Desajuste <5 mil | Reduce la inestabilidad en 40% |

| Plano de referencia | Cruce de múltiples brechas | Un solo plano sólido | Mejora la CMRR en 22dB |

| Terminación | Extremos no tratados | Resistores paralelos de 100Ω | Suprime las reflexiones |

El enlace de PCIe Gen4 de un cliente falló debido a un desajuste de longitud de par de 20 mil. Al volver a enrutar con serpientes, logramos una desviación <3 mil y aprobamos la compatibilidad. Simule siempre las impedancias de modo impar y par—la impedancia diferencial Z0 no es simplemente 2x la impedancia de un solo extremo.

Optimización de la pila de capas para reducir la EMI?

Su PCB emite más RF que un enrutador WiFi. La superposición de capas inteligente silencia la EMI sin costosos recipientes de blindaje.

Separe las capas de señal con planos de tierra, coloque trazas de alta velocidad en capas internas entre tierras y alterne capas de señal / dirección. Use 2-4 mil de prepreg entre capas de señal / plano adyacentes para maximizar el acoplamiento y minimizar las áreas de bucle.

)

Pila de capas de 8 capas optimizada para la EMI

| Capa | Tipo | Propósito |

|---|---|---|

| 1 | Señal | Señales de control de baja velocidad |

| 2 | Tierra | Blindaje de EMI para la capa 3 |

| 3 | Señal | Diferenciales de alta velocidad (10+ Gbps) |

| 4 | Alimentación | Planos de 3,3V/1,8V con condensadores de desacoplamiento |

| 5 | Señal | Señales de reloj de alta velocidad de un solo extremo |

| 6 | Tierra | Camino de retorno para la capa 5 |

| 7 | Alimentación | Planos de 12V/5V |

| 8 | Señal | Componentes analógicos / RF |

Logré una reducción de la EMI de 8 dB en un diseño de DDR4 al flanquear trazas críticas con tierras (capas 2 y 6). Evite enrutar señales de alta velocidad en capas externas donde radian libremente. Las líneas estratificadas enterradas entre planos confinan los campos mejor que las microstrips.

Minimización de muñones de via y optimización de via de señal?

Los muñones de via se comportan como antenas, radiando ruido y distorsionando las señales. Un muñón de 0,5 mm puede arruinar un enlace de 25Gbps.

Use taladrado inverso para eliminar los barriles de via no utilizados, coloque los via <1/8 de la longitud de onda desde los pads y optimice los antipads (8-12 mil más grandes que el taladro). Para señales de alta velocidad críticas, despliegue microvias o taladros láser escalonados para eliminar los muñones por completo.

)

Comparación de técnicas de optimización de via

| Método | Longitud del muñón | Impacto de costo | Velocidad de datos máxima |

|---|---|---|---|

| Via estándar | 1,6 mm | Bajo | 5 Gbps |

| Via ciego/enterrado | 0,2 mm | Alto | 28 Gbps |

| Taladrado inverso | 0,1 mm residual | Medio | 56 Gbps |

| Microvia láser | 0,0 mm | Alto | 112 Gbps |

Al reemplazar los via estándar con microvias láser de 0,15 mm en un diseño de 40Gbps, reduje la pérdida de señal en un 18%. Asegúrese de que la tolerancia de profundidad de taladrado inverso sea ±2 mils—una vez tuve que desechar un lote debido a capas de tierra sobretaladradas. La claridad del antipad es importante: 10 mils alrededor de un via de 8 mil reducen la capacitancia en un 27%.

Errores comunes en el cableado de PCB de alta velocidad y cómo solucionarlos?

Incluso los profesionales cometen estos errores. Reconozca estos pecados de PCB antes de que su placa se convierta en un transmisor de RF de $10k.

Principales errores: impedancia no comprobada (varianza del 20%), señales de alta velocidad no relacionadas entre pares diferenciales, muñones de via que exceden el tiempo de subida de la señal y planos de referencia divididos debajo de trazas críticas. Soluciones incluyen el recálculo de la impedancia, la reruta, el taladrado inverso y la adición de via de costura a través de brechas de plano.

)

Guía de diagnóstico y corrección de errores

| Error | Síntoma | Acción correctiva |

|---|---|---|

| Giros de traza de 90° | Picos de impedancia | Use giros de 45° o arcos |

| Pares diferenciales no coincidentes | Alta tasa de error de bits | Agregue serpientes de coincidencia de longitud |

| No hay via de costura | Hotspots de EMI | Agregue via de tierra cada intervalo λ/10 |

| Cruce de brechas de plano | Reflexiones de señal | Puente las brechas con condensadores de 0,1 μF |

Una vez depuré una placa donde las señales de SPI que se enrutan entre los pares de PCIe causaron un ruido de 3 dB. Separarlos por 40 mils lo resolvió. Siempre reserve un 20% de espacio adicional para las reenrutaciones de alta velocidad—los diseños comprimidos garantizan respins.

Conclusión

Domine el cableado de PCB de alta velocidad a través del control de impedancia, el enrutamiento de pares diferenciales y la reducción de la EMI para prevenir la pérdida de señal y garantizar el cumplimiento. Combine el enrutamiento basado en reglas con simulaciones previas al diseño para evitar respins costosos. Recuerde: una verificación de SIwave de 5 minutos ahorra 50 horas de depuración de laboratorio.