Les défaillances de PCB à haute vitesse coûtent aux ingénieurs des heures inouïes de débogage. Votre conception de pointe s’effondre sous les signaux GHz. Réparons les traces instables, le chaos EMI et les distorsions de signal grâce à des optimisations de câblage stratégiques.

Optimisez le câblage de PCB à haute vitesse en donnant la priorité au contrôle d’impédance (tolérance de 4-6 %), en minimisant les amorces de via avec le fraisage inverse et en utilisant des paires différentielles symétriques. Mettez en œuvre des empilements de couches avec blindage au sol et validez les conceptions avant la production avec Ansys SIwave pour assurer l’intégrité des signaux et la conformité EMI.

Ces techniques séparent les prototypes fonctionnels des poids plume émetteurs de radio. Ci-dessous, je vais disséquer les stratégies d’optimisation critiques testées sur 12 projets à haute vitesse.

Comprendre les défis d’intégrité des signaux dans le câblage de PCB à haute vitesse ?

Avez-vous déjà vu des signaux ressembler au bruit sur votre oscilloscope ? À 5 Gbps et plus, les réflexions et les interférences croisées corrompent les données. Décodons les ennemis invisibles qui sabotent vos signaux.

Les signaux à haute vitesse sont confrontés à des défauts d’impédance (causant des réflexions), à des interférences croisées entre traces parallèles et à des pertes dues à l’effet de peau. Atténuez ces problèmes en maintenant des plans de référence continus, en évitant les coudes à 90° et en gardant les traces inférieures à 1/10ème de la longueur d’onde du signal.

Facteurs critiques impactant la qualité du signal

| Défi | Cause principale | Solution |

|---|---|---|

| Bruit de réflexion | Défauts d’impédance | Faites correspondre l’impédance de la trace à celle du conducteur/récepteur |

| Interférences croisées | Couplage entre traces | Règle d’espacement des traces 3X |

| Atténuation | Pertes diélectriques + pertes de conducteur | Utilisez des matériaux Rogers ultra-basse perte |

| Rebond de masse | Chemins de retour inductifs | Plans de masse solides sous les traces |

L’effet de peau augmente la résistance aux fréquences GHz — des traces larges (8-12 mil) réduisent les pertes. Pour des paires différentielles de 100 Ω, maintenez un espacement de 5 mils avec une largeur de 6 mils sur FR4 (Dk = 4,5). Les interruptions de plans de référence créent des pics d’impédance ; j’ai passé 3 semaines à déboguer une conception 28 GHz pour finalement trouver une interruption de 0,5 mm dans le plan de masse.

Règles de conception pour le routage d’impédance contrôlée ?

Les défauts d’impédance déclenchent des réflexions de signaux pires que l’écho dans un canyon. Votre lien 10 Gbps devient un désordre 1 Gbps. Les règles de routage de précision empêchent cela.

Calculez la largeur/hauteur de la trace à l’aide de solveurs de champ (par exemple, Polar SI9000), maintenez une tolérance d’impédance de ± 5 % et évitez les changements abrupts de largeur. Routez au-dessus de plans de référence continus avec un espacement diélectrique contrôlé pour assurer une impédance caractéristique constante le long de l’ensemble des chemins de signal.

)

Liste de contrôle du contrôle d’impédance

| Paramètre | Impact sur Z0 | Ajustement recommandé |

|---|---|---|

| Augmentation de la largeur de la trace | Abaisse Z0 | Traces plus étroites |

| Épaisseur du diélectrique | Augmente Z0 | Réduisez l’espacement des couches |

| Valeur Er (Dk) | Dk plus bas augmente Z0 | Commutez vers Rogers 4350B |

| Poids du cuivre | Cuivre plus épais abaisse Z0 | Utilisez 0,5 oz de cuivre |

Pour les lignes striées, Z0 ≈ 87 / sqrt (εr + 1,41) * ln (5,98h / (0,8w + t)). Je route les singles 50 Ω avec des traces de 8 mils sur des noyaux FR4 de 10 mils. Lorsque vous êtes obligé de traverser les interruptions de plan, reliez-les avec des condensateurs de couture (0,1 μF) pour maintenir les chemins de retour.

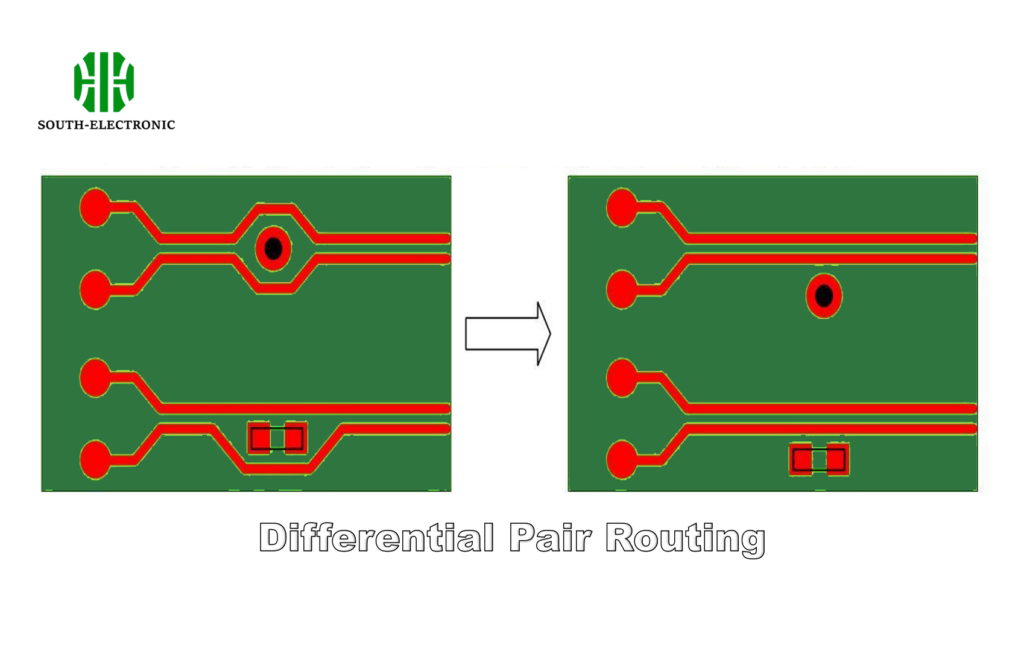

Bonnes pratiques pour le routage de paires différentielles ?

Des paires différentielles non appariées déforment les signaux comme une suspension cassée. Le jitter d’horloge explose. La symétrie est non négociable.

Maintenez un espacement de paire inférieur à 2 fois la largeur de la trace, faites correspondre les longueurs de trace dans les 5 mils et routez de manière symétrique. Utilisez des serpentines de réglage de longueur aux extrémités des récepteurs et minimisez les interruptions de plan de référence sous les paires pour maintenir la réjection de bruit de mode commun.

)

Matrice d’optimisation des paires différentielles

| Paramètre | Mauvaise pratique | Pratique optimale | Avantage |

|---|---|---|---|

| Espacement | 3 fois la largeur de la trace | 1 fois la largeur de la trace | Réduit l’EMI de 12 dB |

| Appariement de longueur | Défaut de 50 mils | Défaut inférieur à 5 mils | Réduit le jitter de 40 % |

| Plan de référence | Traverse plusieurs interruptions | Plan solide unique | Améliore le CMRR de 22 dB |

| Termination | Extrémités non traitées | Résistances parallèles 100 Ω | Supprime les réflexions |

Un client a vu son lien PCIe Gen4 échouer en raison d’un défaut d’appariement de longueur de paire de 20 mils. En réacheminant avec des serpentines, nous avons obtenu une déviation inférieure à 3 mils et avons passé la conformité. Simulez toujours les impédances de mode impair/pair — l’impédance différentielle Z0 n’est pas simplement 2 fois l’impédance à un seul bras.

Optimisation de l’empilement de couches pour réduire l’EMI ?

Votre PCB émet plus de RF qu’un routeur WiFi. Un empilement de couches intelligent silencie l’EMI sans coûteuses boîtes de blindage.

Séparez les couches de signal avec des plans de masse, placez les traces à haute vitesse sur les couches internes entre les masses et alternez les couches de signal/direction. Utilisez 2-4 mils de préimprégné entre les couches de signal/plan adjacentes pour maximiser le couplage et minimiser les aires de boucle.

)

Empilement de couches 8 couches optimisé pour l’EMI

| Couche | Type | Objectif |

|---|---|---|

| 1 | Signal | Signaux de contrôle à basse vitesse |

| 2 | Masse | Blindage EMI pour la couche 3 |

| 3 | Signal | Differentiels à haute vitesse (10+ Gbps) |

| 4 | Alimentation | Plans 3,3 V/1,8 V avec condensateurs de découplage |

| 5 | Signal | Signaux d’horloge à haute vitesse à un seul bras |

| 6 | Masse | Chemin de retour pour la couche 5 |

| 7 | Alimentation | Plans 12 V/5 V |

| 8 | Signal | Composants analogiques/RF |

J’ai obtenu une réduction de 8 dB de l’EMI dans une conception DDR4 en flanquant les traces critiques avec des masses (couches 2 et 6). Évitez de router les signaux à haute vitesse sur les couches extérieures où ils rayonnent librement. Les lignes striées enterrées entre les plans confinent mieux les champs que les microbandes.

Minimisation des amorces de via et optimisation des vias de signal ?

Les amorces de via se comportent comme des antennes, rayonnant du bruit et distordant les signaux. Une amorce de 0,5 mm peut ruiner un lien 25 Gbps.

Utilisez le fraisage inverse pour supprimer les barils de via non utilisés, placez les vias à moins de 1/8 de la longueur d’onde du signal à partir des pads et optimisez les antipads (8-12 mils plus grands que le forage). Pour les signaux critiques, déployez des microvias ou des perforations laser décalées pour éliminer complètement les amorces.

)

Comparaison des techniques d’optimisation des vias

| Méthode | Longueur d’amorce | Impact sur le coût | Débit de données maximal |

|---|---|---|---|

| Via traversant standard | 1,6 mm | Faible | 5 Gbps |

| Via aveugle/enterré | 0,2 mm | Élevé | 28 Gbps |

| Fraisage inverse | 0,1 mm résiduel | Moyen | 56 Gbps |

| Microvia au laser | 0,0 mm | Élevé | 112 Gbps |

Dans une conception 40 Gbps, le remplacement des vias traversants par des microvias au laser de 0,15 mm a réduit les pertes de signal de 18 %. Assurez-vous que la tolérance de profondeur de fraisage inverse est de ± 2 mils — j’ai dû jeter un lot en raison de couches de masse surexcavées. La tolérance d’antipad compte : 10 mils autour d’un via de 8 mils réduisent la capacité de 27 %.

Erreurs communes de câblage de PCB à haute vitesse et comment les corriger ?

Même les professionnels commettent ces erreurs. Reconnaissez ces péchés de PCB avant que votre carte ne devienne un émetteur RF de 10 000 $.

Erreurs principales : impédance non vérifiée (variation de 20 %), signaux non apparentés entre paires différentielles, amorces de via dépassant le temps de montée du signal et plans de référence divisés sous des traces critiques. Les correctifs incluent le recalculation de l’impédance, la réacheminement, le fraisage inverse et l’ajout de vias de couture à travers les interruptions de plan.

)

Guide de diagnostic et de correction d’erreurs

| Erreur | Symptôme | Action corrective |

|---|---|---|

| Coudes de trace à 90° | Pics d’impédance | Utilisez des coudes à 45° ou des courbes |

| Paires différentielles non appariées | Taux d’erreur élevé | Ajoutez des serpentines d’appariement de longueur |

| Pas de vias de couture | Points chauds EMI | Ajoutez des vias de masse tous les 1/10 de la longueur d’onde |

| Traverse des interruptions de plan | Réflexions de signal | Reliez les interruptions avec des condensateurs de 0,1 μF |

J’ai débogué un circuit imprimé où les signaux SPI routés entre des paires PCIe ont causé 3 dB de bruit. Les séparer de 40 mils a résolu le problème. Réservez toujours 20 % d’espace supplémentaire pour les réacheminements à haute vitesse — des conceptions compressées garantissent des rééditions.

Conclusion

Maîtrisez le câblage de PCB à haute vitesse grâce au contrôle d’impédance, au routage différentiel et aux empilements de couches réduisant l’EMI pour prévenir les pertes de signal et assurer la conformité.