Avez-vous déjà perdu des semaines à déboguer un circuit imprimé pour finalement trouver une mauvaise connexion ? Une liste de connexions de circuit imprimé vous évite ce cauchemar en agissant comme l’ADN du circuit. Laissez-moi vous expliquer pourquoi ce fichier texte discret constitue la base de votre conception.

Une liste de connexions de circuit imprimé est un fichier texte ASCII définissant les connexions électriques entre les broches des composants. Elle relie les schémas et l’agencement physique tout en permettant les simulations et la vérification automatique des erreurs, ce qui en fait la source unique de référence pour le fonctionnement du circuit imprimé.

Bien que comprendre les listes de connexions puisse paraître technique, maîtriser leur rôle peut éviter des erreurs de conception catastrophiques. Analysons leur fonctionnement à travers différents systèmes et étapes.

Comment les outils EDA génèrent-ils une liste de connexions ?

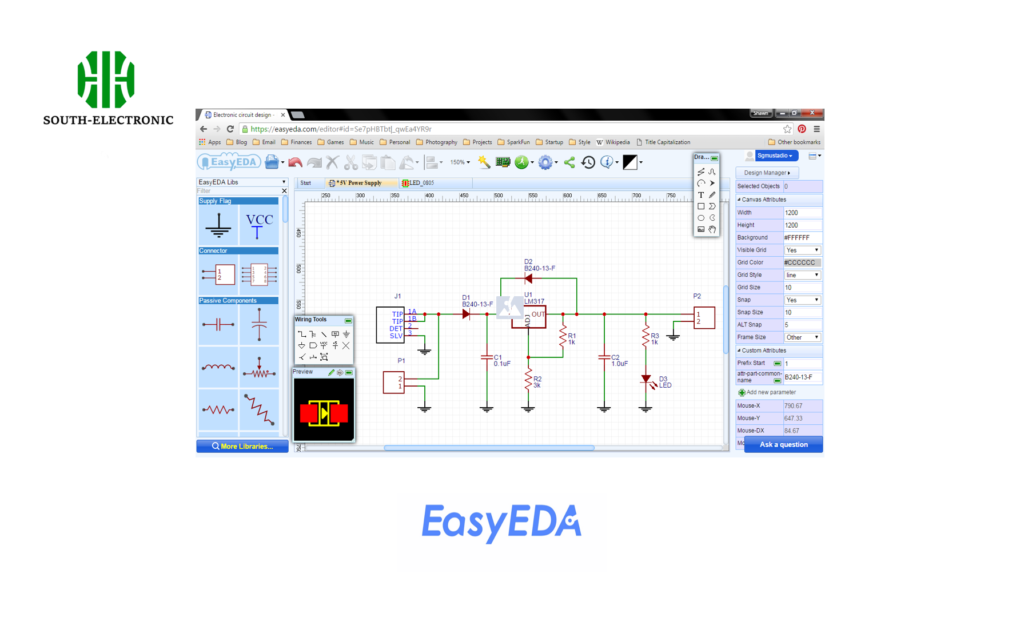

Voyez votre schéma se transformer en instructions lisibles par machine. Les outils EDA génèrent des listes de connexions en interprétant vos dessins comme des connexions mathématiques, mais tous les outils ne le font pas de la même manière.

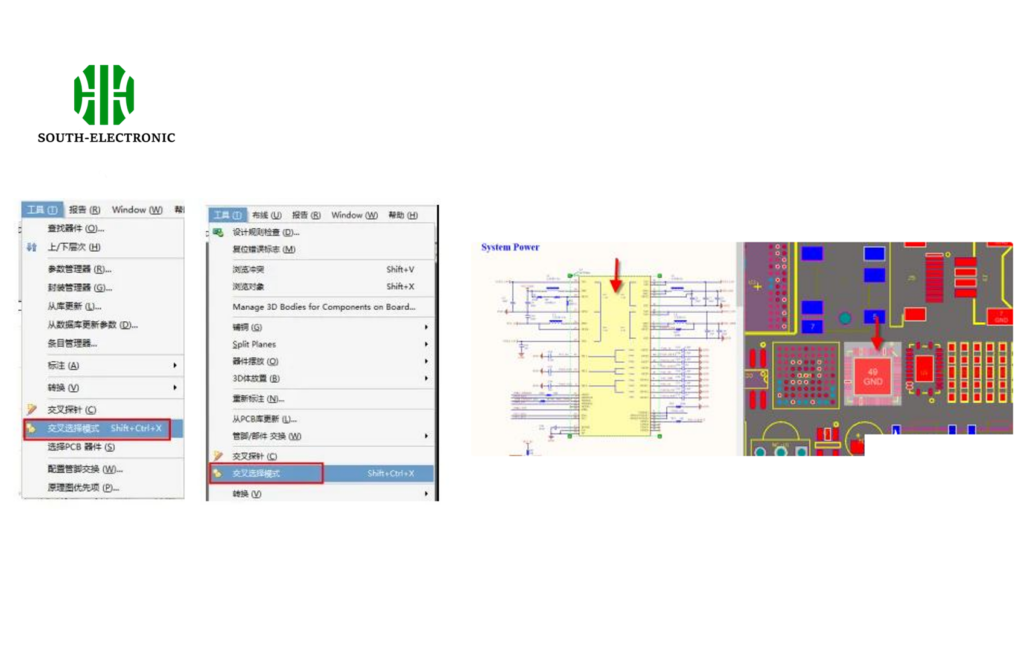

Les logiciels EDA comme Altium Designer créent des listes de connexions en analysant les broches et les fils des composants dans les schémas. Les outils modernes ajoutent des métadonnées telles que les classes de réseaux et les paires différentielles pour faciliter l’implantation.

Processus de génération de listes de réseaux

La plupart des outils suivent trois étapes :

| Étape | Action | Points de contrôle critiques |

|---|---|---|

| 1. Analyse schématique | Lecture des symboles des composants et des connexions des fils | Vérification de la correspondance du nombre de broches des symboles avec les empreintes |

| 2. Validation des règles électriques | Vérification des courts-circuits/réseaux ouverts | Signalisation des broches d’alimentation non connectées |

| 3. Exportation du format | Enregistrement aux formats SPICE/EDIF/autres | Confirmation de la compatibilité avec l’outil d’implantation cible |

La clé est la cohérence. Le mois dernier, le circuit imprimé de mon collègue est tombé en panne car son outil EDA utilisait la lettre « gnd » en minuscules alors que l’implantation attendait « GND ». Vérifiez toujours la casse des noms de réseau en amont.

Pourquoi la vérification de la liste des réseaux est-elle essentielle avant le routage du PCB ?

Ignorer la vérification de la liste des réseaux revient à construire sans plans. Selon des études de l’IEEE, 63 % des erreurs post-routage sont dues à des listes de réseaux non vérifiées.

La vérification de la liste des réseaux compare les connexions schématiques avec le fichier généré et les règles cibles. Elle détecte les incohérences, comme les broches échangées ou les composants manquants, avant une production coûteuse.

Domaines de vérification courants

Créez une liste de contrôle correspondant aux priorités suivantes :

| Type de vérification | Outils utilisés | Erreurs critiques détectées |

|---|---|---|

| Électrique | SPICE, HyperLynx | Courts-circuits, nœuds flottants |

| Logique | FormalCheck, scripts personnalisés | Incohérences de direction du signal |

| Physique | Comparaison CAO, DIFF | Incohérences de nombre de broches d’empreinte |

J’ai déjà vu un prototype à 25 000 $ mis au rebut à cause d’une ligne de données DDR4 connectée à une mauvaise banque. Détectée instantanément lors des vérifications de netlistes, mais invisible dans les schémas. Vérifiez trois fois, prototypez une fois.

Netlistes SPICE vs EDIF : Quel format convient à votre projet ?

Choisir le mauvais format, c’est comme parler français à Tokyo. Les netlistes SPICE et EDIF servent des maîtres différents ; sachez lequel vos outils comprennent.

Utilisez les netlistes SPICE (.cir) pour la simulation de circuits et l’analyse analogique. Choisissez EDIF (.edf) pour le routage de circuits imprimés et l’intégration de systèmes numériques.

Guide de comparaison des formats

| Factor | SPICE | EDIF |

|---|---|---|

| Idéal pour | Simulations | Collaboration multi-outils |

| Types de données | Paramètres analogiques | Données de conception hiérarchiques |

| Prise en charge des outils | LTspice, PSpice | Cadence Allegro, Altium |

| Lisibilité | Convivial | Optimisé pour la machine |

L’année dernière, lors de la conception d’une carte IoT à signaux mixtes, j’ai utilisé SPICE pour la validation des capteurs et EDIF pour le routage, prouvant ainsi la nécessité des deux formats pour les hybrides. Adaptez le format à votre phase actuelle.

7 erreurs de netlist qui pourraient ruiner votre prototype de PCB

Avez-vous déjà vu une faute de frappe de 10 $ ruiner une carte de 10 000 $ ? Ces erreurs silencieuses de netlist échappent aux contrôles de base.

Les principales erreurs fatales de listes de connexions incluent les paires différentielles permutées, les noms de connexions dupliqués, les connexions d’alimentation manquantes, le mappage de broches incorrect, les activations de puces non connectées, les incompatibilités entre symboles et empreintes et les caractères spéciaux non protégés.

Liste de contrôle de prévention des erreurs

| Type d’erreur | Méthode de détection | Conseil de prévention |

|---|---|---|

| Permutations de broches | Comparaison avec les fiches techniques | Mise en évidence des connexions critiques dans les schémas |

| Connexions manquantes | Outils de vérification croisée | Utilisation de l’ERC avec des règles strictes |

| Conflits de noms | Étiquetage unique des connexions | Adopter la dénomination « _ » |

Un trait de soulignement manquant dans « 3V3_Audio » par rapport à « 3V3Audio » a autrefois fusionné les rails d’alimentation, provoquant la panne des amplificateurs opérationnels. Ne sous-estimez jamais les conventions de nommage.

Conclusion

Les listes de connexions PCB transforment des circuits abstraits en plans constructibles. En choisissant les bons formats, en effectuant des vérifications rigoureuses et en traquant les erreurs sournoises, vous ferez de cette étape technique votre arme secrète en matière de fiabilité.