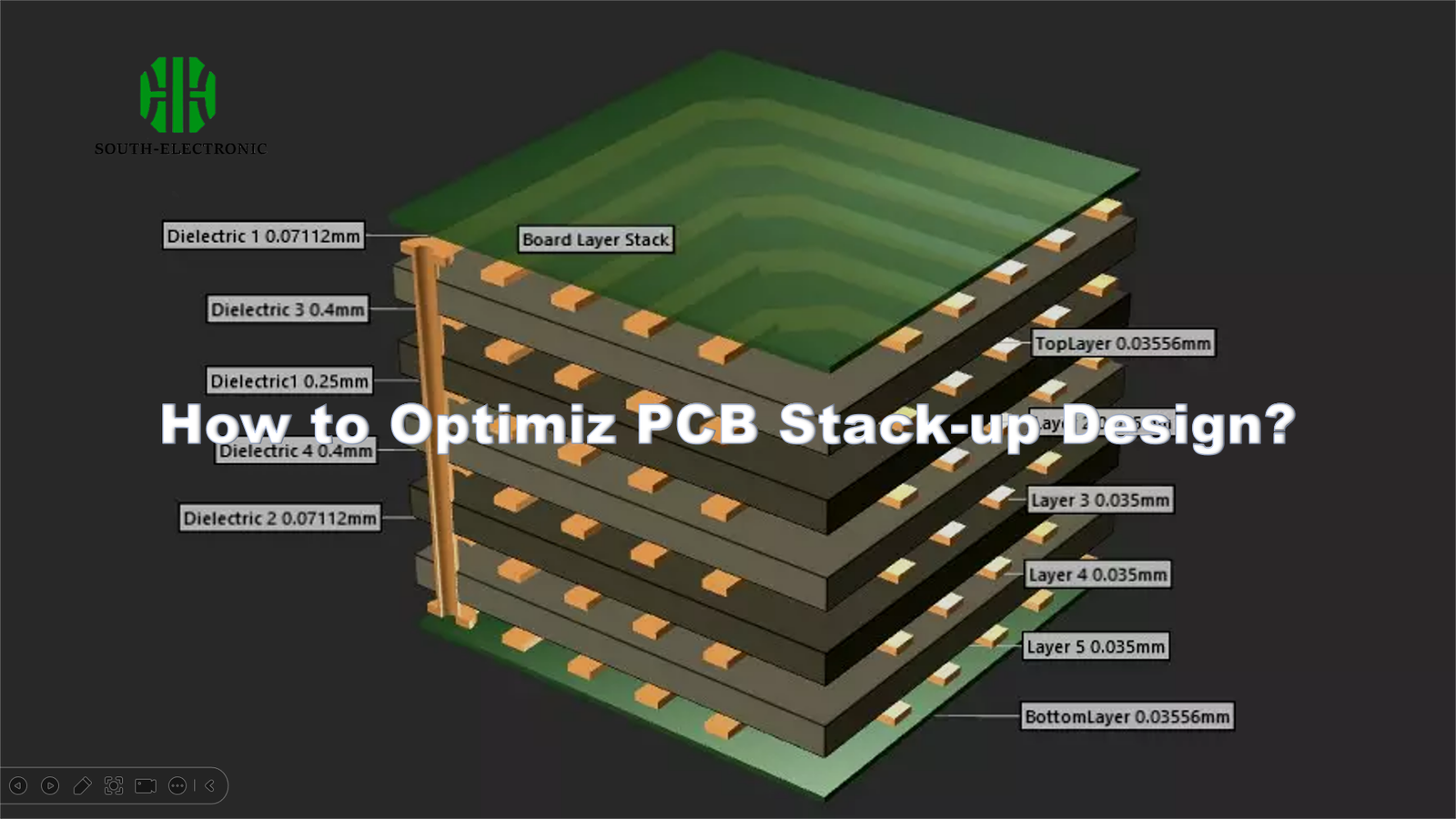

Ваш последний проект печатной платы потерпел неудачу из-за перегрева? Вы потратили 3000 долларов на ненужные 12-слойные платы? Я видел, как 63% команд по разработке оборудования допускали критические ошибки в стеке перед тестированием прототипов. Давайте исправим это.

Оптимальное укладывание печатных плат[^1] использует гибридные материалы для критических слоев, подбирает количество слоев[^2] для сложности сигнала и применяет симметричные конструкции для предотвращения коробления. Моя команда добилась снижения затрат на 25% за счет замены подложек[^3] без ущерба для контроля импеданса.

Эти пять стратегий стекирования образуют пошаговую структуру. Начиная с планирования количества слоев и заканчивая решениями по ЭМП, каждое решение одинаково влияет на производственные затраты и надежность сигнала.

Как определить подходящее количество слоев для стекирования печатной платы?

6-слойная плата стоила 180 долларов в прошлом квартале. Наша новая 4-слойная конструкция с оптимизированной маршрутизацией выполняет ту же работу за 112 долларов. Когда вам НУЖНЫ дополнительные слои?

Количество слоев зависит от типов сигналов: используйте 4 слоя для несимметричных сигналов ниже 2 ГГц. Требуется 6+ слоев при смешивании ВЧ, цифровых и силовых цепей или использовании ≥3 дифференциальных пар, требующих изоляции.

)

Три ключевых фактора оптимизации слоев

| Фактор | Подходящие корпуса с 4 слоями | Требуемые корпуса с 6 слоями |

|---|---|---|

| Типы сигналов | Несимметричный DC/1 ГГц цифровой | Смешанный ВЧ+цифровой+аналоговый |

| Размер платы | ≥70 мм x 90 мм | <50 мм x 50 мм (требуется HDI) |

| Ограничения по бюджету | Стоимость прототипа <$200/ед. | Оптимизация спецификации конечного продукта |

Я создаю прототип с FR-4 на 4 слоях, затем проверяю с помощью TDR, требуют ли несоответствия импеданса обновления слоев. Последняя конструкция блока питания показала, что 8 слоев не нужны — замена на 2-унциевую медь на внутренних слоях сэкономила 18% материальных затрат.

Как выбрать основные материалы для высокочастотного и обычного проектирования печатных плат?

RO4350B стоит в 7 раз дороже стандартного FR-4. Но когда я использовал его только на критических слоях радара 24 ГГц, потери в системе снизились на 41%, при этом материальные затраты остались неизменными на 84%.

Гибридное стекирование[^4] работает лучше всего: используйте материалы Rogers/Isola HF только на слоях RF (≤4). Оставьте другие слои как FR-4. Убедитесь, что несоответствие КТР <3ppm/°C между соседними диэлектриками, чтобы избежать расслоения.

)

Критерии выбора материала[^5] Таблица

| Применение | Рекомендуемый материал | Dk @10 ГГц | Тангенс угла потерь | Стоимость за м² |

|---|---|---|---|---|

| Антенна 5G mmWave | Rogers RO4835 | 3,48 | 0,0037 | 380 $ |

| Шина памяти DDR4 | Isola I-Speed | 3,87 | 0,007 | 270 $ |

| 12 В силовая плоскость | Shengyi S1000-2 | 4,3 | 0,02 | 42 $ |

Мы объединяем моделирование ЭМ и пробные партии: сначала модель с идеальными материалами, затем понижаем некритичные слои, пока целостность сигнала не достигнет предела допуска 15%. Такой подход сократил расходы на материалы на 31% в последнем проекте WiFi 6E.

Какие ключевые параметры требуются для управления импедансом[^6] многослойной печатной платы?

Несоответствие в 92 Ом разрушило наш прототип. Теперь я применяю: дисперсия веса меди ≤0,2 унции, допуск толщины диэлектрика ±8%, дисперсия Dk ±0,15.

Критические параметры: 1) Толщина сердечника/оболочки 2) Коэффициент компенсации травления 3) Постоянство Dk/Df на панелях 4) Равномерность покрытия. Поддерживайте отклонение импеданса ≤5% с помощью поперечного сечения и выборочных проверок TDR.

Протокол управления импедансом

| Параметр | Метод измерения | Допустимый диапазон | Метод регулировки |

|---|---|---|---|

| Толщина диэлектрика[^7] | Микроскопия поперечного сечения | ±8% от номинала | Регулировка препрега ламината |

| Шероховатость меди | Профилометр | Rz ≤5 мкм | Электрополировка |

| Постоянство Dk | Испытание с зажатой полосковой15 на партию | Аудит поставщика материалов |

Я сотрудничаю с производителями на раннем этапе, предоставляя целевые значения импеданса для отдельных слоев вместо общих спецификаций. Для дифференциальных пар 100 Ом на слое 3–4: укажите точную толщину диэлектрика (0,204 мм ± 0,015 мм), используйте обратные вычисления для получения приемлемых весов меди и коэффициентов травления.

Как снизить общую стоимость за счет оптимизации структуры стекирования?

Сокращение с 14 до 10 слоев снизило себестоимость производства на 37%, но только после того, как мы доказали, что симметричные стеки предотвращают коробление в печах оплавления с помощью термического моделирования.

Три способа снизить стоимость:

1) Симметричное распределение меди[^8]

2) Замените скрытые переходные отверстия на разнесенные микропереходные отверстия[^9]

3) Используйте внутренние силовые слои 2oz, чтобы исключить 2 сигнальных слоя. Достигните 40% снижения стоимости, сохранив функциональность 8 слоев.

)

Контрольный список оптимизации стека

| Методика | Влияние на стоимость | Сложность реализации | Снижение риска |

|---|---|---|---|

| Объединение слоев питания | -15% за объединение | Средняя | Увеличить зазор плоскости |

| Гибридный стек материалов[^10] | -22% стоимости материала | Высокая | Проверка соответствия КТР |

| Устранение переходов в контактной площадке | -8% стоимости сверления | Низкая | Перераспределение компонентов |

Практический пример: для промышленного контроллера переход с 12-слойной полностью FR4 на 8-слойную гибридную (Rogers + IT-180A) сохранил тепловые характеристики. Согласованное использование панели с 65% до 89% с помощью зеркальных стековых конструкций, достигнув 29% общего снижения затрат.

Как избежать перекрестных помех и потерь сигнала в высокоскоростной конструкции стекирования печатных плат?

Чрезмерные потери 3 дБ на частоте 28 ГГц? Наш анализ выявил неправильное заземляющее соединение через интервал. Теперь я применяю: ортогональную маршрутизацию соседних сигнальных слоев, острова питания вместо полных плоскостей вблизи радиочастотных трасс.

Предотвращаем перекрестные помехи через: 1) правило зазора 3 Вт[^11] 2) чередующиеся слои заземления между высокоскоростными сигналами 3) изменение толщины диэлектрика ≤15%. Для 56 Гбит/с PAM4 разверните инвертированную микрополосковую схему с предварительно пропитанным Dk <3,3.

Укладка слоев управления ЭМП

| Угроза | Решение для стека | Метод проверки |

|---|---|---|

| Краевое излучение | симметричный стек 2-4-2[^12] | Сканирование ЭМП камеры >3 м |

| Синфазный шум | Разделенные плоскости питания со сшиванием | Анализ S-параметров VNA |

| Резонанс через заглушку | Обратное сверление за пределами диаметра 1,5x через отверстие | TDR с временем нарастания 35 пс |

Окончательное правило проектирования: назначайте критические сигналы слоям 2-3 и 6-7 в 8-слойных платах. Это обеспечивает смежные плоскости заземления, избегая проблем с поглощением влаги внешним слоем. Наша проверка PCIe Gen5 x16 показала улучшение на 0,8 дБ/дюйм при использовании этой конфигурации.

Заключение

Для баланса производительности и стоимости требуются гибридные материалы, оптимизация количества слоев и строгие протоколы импеданса. Реализуйте эти стратегии стекирования, чтобы сократить расходы на печатные платы на 25-40 % без ущерба для целостности сигнала в высокочастотных конструкциях.

[^1]: Изучение передовых методов стекирования печатных плат поможет вам избежать дорогостоящих ошибок и оптимизировать свои конструкции для производительности и стоимости.

[^2]: Понимание того, как определить правильное количество слоев, может существенно повлиять на производительность и экономическую эффективность вашей печатной платы.

[^3]: Изучение замены подложки может привести к экономии средств и повышению производительности в ваших проектах печатных плат.

[^4]: Изучите эту ссылку, чтобы понять, как гибридное укладывание может оптимизировать проект вашей печатной платы для производительности и экономической эффективности.

[^5]: Узнайте основные критерии выбора материалов для повышения производительности и надежности вашей печатной платы.

[^6]: Узнайте о контроле импеданса, чтобы гарантировать, что ваши проекты печатных плат соответствуют стандартам производительности и избегают дорогостоящих несоответствий.

[^7]: Понимание толщины диэлектрика имеет решающее значение для достижения точного контроля импеданса в проекте печатной платы, обеспечивая оптимальную производительность.

[^8]: Изучение этой темы показывает, как симметричное распределение меди может значительно снизить затраты, одновременно повышая надежность печатной платы.

[^9]: Изучение ступенчатых микроотверстий может помочь вам оптимизировать компоновку печатной платы для повышения производительности и экономической эффективности.

[^10]: Узнайте, как гибридные материалы могут значительно снизить затраты, сохранив при этом производительность. линией | ±0.в конструкциях печатных плат.

[^11]: Узнайте о правиле зазора 3 Вт для предотвращения перекрестных помех сигнала и обеспечения высокой скорости работы печатных плат.

[^12]: Узнайте о преимуществах симметричного стека 2-4-2 для снижения краевого излучения и улучшения характеристик ЭМП.