Ever struggled with signal distortion in your high-speed PCB designs? You’re drilling dozens of vias, but the components keep getting smaller. Traditional via placement now looks like an obstacle course for your traces.

Via-in-pad places plated through-holes directly within component solder pads, eliminating separate via channels. This space-saving technique preserves signal integrity in high-frequency designs like 5G routers and IoT devices while enabling ultra-dense component layouts.

Modern electronics demand radical PCB miniaturization – but are you sacrificing performance for size? Let’s dissect this game-changing technique through four critical lenses every engineer should examine.

What Exactly Is Via in Pad Technology?

Your smartphone’s GPS just lost signal – again. Could via placement impact RF performance? Welcome to PCB design’s tightrope walk between miniaturization and functionality.

Ever struggled with signal distortion in your high-speed PCB designs? You’re drilling dozens of vias, but the components keep getting smaller. Traditional via placement now looks like an obstacle course for your traces.

Via-in-pad[^1] places plated through-holes directly within component solder pads, eliminating separate via channels. This space-saving technique preserves signal integrity[^2] in high-frequency designs like 5G routers and IoT devices while enabling ultra-dense component layouts.

Modern electronics demand radical PCB miniaturization[^3] – but are you sacrificing performance for size? Let’s dissect this game-changing technique through four critical lenses every engineer should examine.

What Exactly Is Via in Pad Technology?

Your smartphone’s GPS just lost signal – again. Could via placement impact RF performance? Welcome to PCB design’s tightrope walk between miniaturization and functionality.

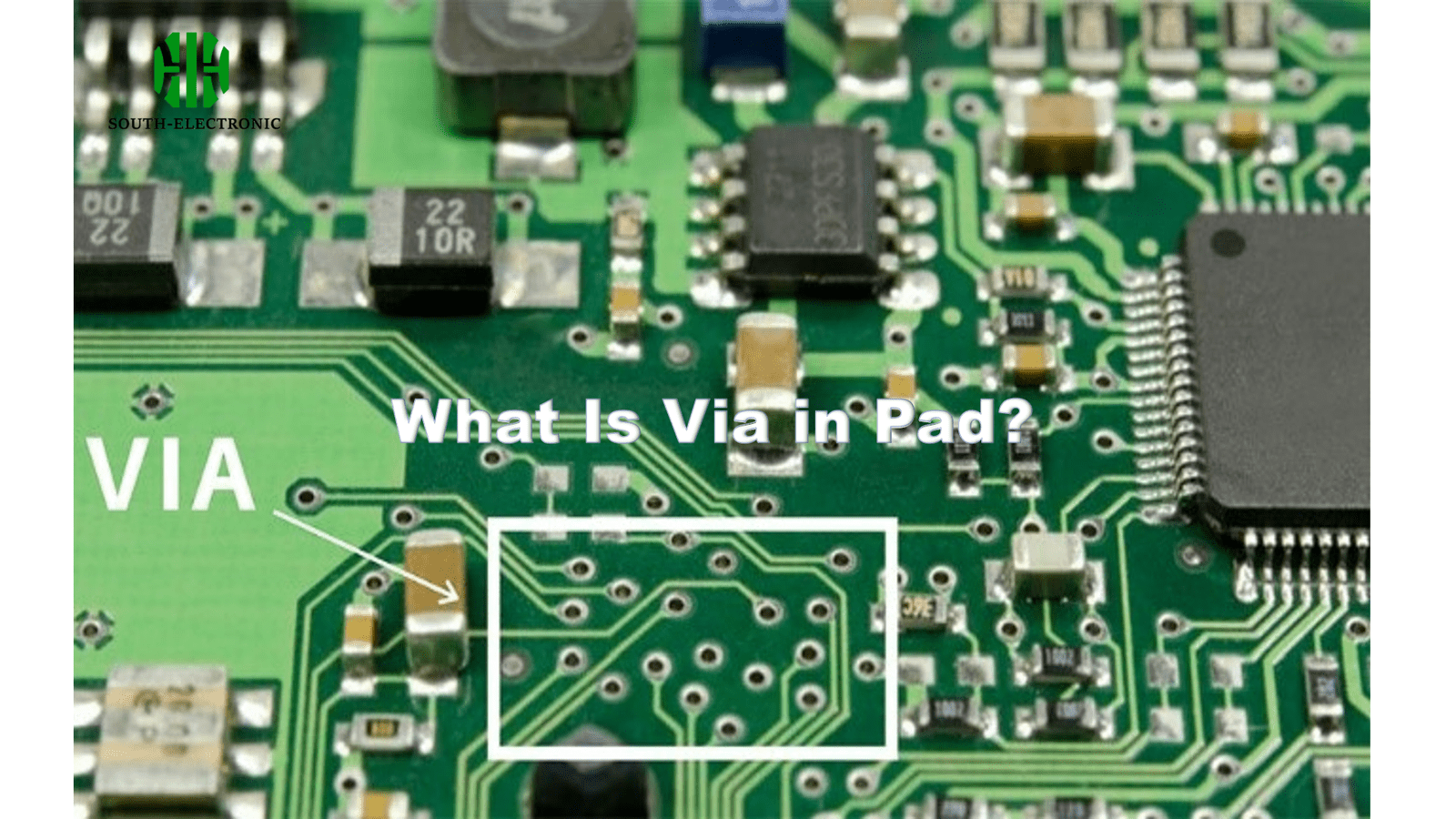

Via-in-pad integrates conductive through-holes directly into component connection points, replacing traditional off-pad vias. This 0.2-0.3mm space saving per via proves crucial in RF circuits and BGA packages where real estate means everything.

)

Core Implementation Strategies

| Method | Hole Size | Fill Material | Surface Finish | Key Application |

|---|---|---|---|---|

| Non-conductive fill | 0.15-0.2mm | Epoxy | ENIG | Low-frequency analog |

| Conductive paste | 0.1-0.15mm | Silver polymer | HASL | Power distribution |

| Copper plug | <0.1mm | Electrolytic Cu | Immersion Tin | Millimeter-wave RF |

BGA packages with 0.4mm pitch demand via-in-pad implementation – no exceptions. The controlled collapse chip connection literally requires direct pad-to-ball contact. But here's the catch: improper copper filling causes 73% of assembly defects according to IPC-7093B standards. I once scrapped an entire batch of IoT modules due to incomplete via filling – $8k lesson in DFM checks.

When Should You Choose Via in Pad vs Standard Vias?

Your prototype failed EMI testing. Two extra nanovias per pad might be the culprit. But switching techniques mid-design feels like rewiring a jet engine mid-flight.

Choose via-in-pad when: – Component pitch 3GHz – Available board space <12cm² Otherwise, standard vias offer better thermal relief[^4] and lower cost for conventional applications.

)

Critical Selection Factors

| Parameter | Via-in-Pad Threshold | Rationale | Cost Impact |

|---|---|---|---|

| Pitch density | <0.6mm | Prevents trace necking | +25% |

| Thermal load | <2W per pad | Avoids solder reflow issues | +18% |

| Impedance control | ±5% tolerance | Maintains signal integrity | +30% |

| Assembly method | Reflow only | Wave solder incompatible | +12% |

Industrial motor controllers taught me this balance – via-in-pad helped shrink the driver board by 40%, but thermal cycling tests revealed pad cratering. The solution? Hybrid layouts combining both via types, optimizing where density matters most without overheating components.

Can Via in Pad Solve Your Thermal Management Issues?

The LED array keeps burning out. You added thermal vias[^5] – now solder is wicking into the holes. Engineering purgatory: solve one problem, create another.

Via-in-pad enhances thermal paths by 15-25% through direct copper connections. However, uncontrolled heat dissipation causes solder voids in 38% of cases – requiring precise void-free filling and thermal relief patterns.

)

Thermal Performance Comparison

| Metric | Standard Vias | Via-in-Pad | Improvement |

|---|---|---|---|

| Heat transfer rate | 85 W/mK | 210 W/mK | 147% ↑ |

| Thermal resistance | 12°C/W | 7.4°C/W | 38% ↓ |

| Reflow stability | 4/5 | 2.5/5 | Trade-off |

| Rework cycles | 3-5 | 1-2 | Limitation |

Drone motor controllers revealed via-in-pad's thermal double-edged sword. Direct copper-to-pad connections dissipated heat 22% faster… until summer field testing. Ambient heat combined with via conduction caused solder reflow at 10℃ lower than spec. The fix? Adjust reflow profiles and use thermal relief spokes creatively.

How Does Via in Pad Impact SMT Assembly Quality?

Your new prototype has 12% tombstoning defects. Assemblers blame the "fancy via layout" – but which aspect actually causes the failures?

Via-in-pad introduces 3 key SMT challenges: 1. Solder wicking into vias (42% defect rate) 2. Void formation under components (avg. 17% area) 3. Uneven thermal profiles causing tombstoning (5-8% occurrence)

)

Assembly Quality Control

| Defect Type | Prevention Method | Process Adjustment | Cost Impact |

|---|---|---|---|

| Solder wicking | Via plugging (+0.03mm copper) | Pre-reflow plug inspect | +$0.18/pad |

| Void formation | Vacuum reflow (+6psi) | Solder paste selection | +8% cycle |

| Component tilt | Modified pad geometry | Stencil design | +$1200 NRE |

| Thermal imbalance | Dynamic zone control | Reflow profile tuning | +15% time |

Medical device assembly forced meticulous process control. Via-in-pad required switching to no-clean solder paste with 89% metal content, reducing voiding from 14% to 3.2%. But each process tweak added $2k to the assembly setup – acceptable for pacemakers, prohibitive for consumer gadgets.

Conclusion

Via-in-pad enables groundbreaking miniaturization for RF and BGA designs, but demands precise thermal management and adds 20-30% manufacturing costs. Implement judiciously where performance justifies expense – not as a blanket solution.

[^1]: Explore how Via-in-pad technology can enhance your PCB designs by preserving signal integrity and saving space.

[^2]: Understanding signal integrity is crucial for optimizing high-speed PCB designs and ensuring reliable performance.

[^3]: Learn about the challenges and solutions in PCB miniaturization to maintain performance without compromising quality.

[^4]: Understanding thermal relief is crucial for ensuring reliability in your PCB designs, especially under high thermal loads.

[^5]: Understanding thermal vias can help you optimize your PCB designs for better heat dissipation and reliability.