Designing an 8-layer PCB? Don’t let complex rules ruin your project. Failed stackups cause noise and signal loss. Learn these essential rules to save your design time.

Key rules for 8-layer PCB stackup[^1] include: Place four signal layers between ground/power planes for shielding. Maintain symmetry to prevent warping. Keep high-speed signals adjacent to reference planes for EMI control[^2]. Use wider traces for power distribution. Proper stackup reduces crosstalk[^3] by 60%. Follow industry standards like IPC-2221.

These foundations matter. Now learn how to apply them effectively in different configurations. Your next design decision could save weeks of troubleshooting.

What Are the Most Common 8-Layer PCB Stackup Configurations?

Picking wrong stackups creates signal disasters. Noise and interference follow. Discover battle-tested configurations I use daily.

2 dominant stackups work for 90% of designs. Type 1: Signal-GND-Signal-PWR-GND-Signal-PWR-Signal. Type 2: GND-Signal-PWR-Signal-Signal-PWR-Signal-GND. Both options give balanced EMI performance.

Which Configuration Should You Choose?

-

High-Speed Digital Designs: Use Type 1 stackup

- Inner signal layers (3 & 6) get dual reference planes

- 0.1mm dielectric between layers 2-3 and 6-7

- Best for >1Ghz signals

-

Mixed Signal Applications: Choose Type 2

- Dedicated power islands (layers 2 & 7)

- Separate analog/digital grounds

| Configuration | Best For | Impedance Stability | Power Noise |

|---|---|---|---|

| Type 1 | DDR4/PCIe/HF signals | Excellent | Moderate |

| Type 2 | RF/Analog systems | Good | Low |

I’ve built medical devices using Type 2 layout. The separated grounds prevented ADC noise issues. Always keep symmetry: balance copper weights across center axis. For six-layer boards needing upgrades, add two copper planes near the core. Avoid sandwiching power between signal layers without GND reference. Your return current paths matter most.

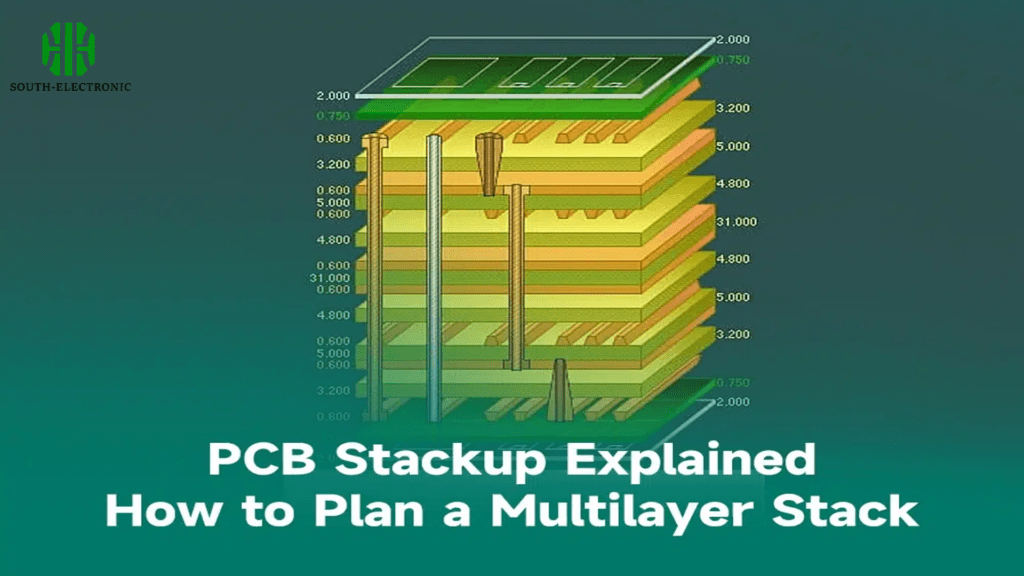

How to Calculate Impedance & Thickness in Your 8-Layer Stackup?

Guessing impedance values destroys signal integrity. Reflections occur. Match calculations to manufacturing reality with these steps.

Use dielectric constant (Dk)[^4] of your material. Measure trace width/spacing. Maintain 50Ω single-ended traces. Pair differential traces at 100±7Ω. I recommend Saturn PCB Toolkit[^5] for free calculations.

Layer Thickness Formula Table

Standard 1.6mm board thickness works best. Follow this structure:

| Layer Position | Material | Thickness (mm) | Copper Weight (oz) |

|---|---|---|---|

| L1 (Top) | Prepreg | 0.13 | 1 |

| L2/L3 | Core | 0.25 | 0.5 |

| L4/L5 | Substrate | 0.71 | 1 |

| L6/L7 | Core | 0.25 | 0.5 |

| L8 (Bottom) | Prepreg | 0.13 | 1 |

- Critical Calculation Rules:

- Microstrip impedance: Use Dk≈4.2 for FR4

- Stripline: Trace-to-plane distance = 3x trace width

- Power planes: Allow 35μm copper minimum

My drone controller project failed initially. Why? I ignored cross-talk calculations[^6] between layers 4 and 5. Recalculated with 0.2mm prepreg insulation. Solved interference. Validate values with your PCB vendor pre-production.

8-Layer PCB Cost Drivers: How to Save 20% Without Sacrificing Quality?

Wasting money on avoidable features? Hidden expenses pile up. Identify costs before finalizing your stackup choices. I saved $4700 on production.

Material choice accounts for 40% of costs. Panel utilization boosts savings. Eliminate special via types when possible. Simple changes cut prices by 15-30%.

Breakdown of Cost Saving Strategies

Three impactful changes work best:

| Cost Driver | Standard Price | After Savings | Method |

|---|---|---|---|

| FR4 Material | Base Price | -18% | Use 0.25mm cores instead of 0.2mm |

| Panel Utilization | 100% | +15 boards | Adjust size < 10% of panel |

| Drill Time | 100% | -35% | Limit microvia count below 200 |

-

Material Optimization

Switch from Rogers to Isola FR408HR saves $12/layer. Avoid exotic copper weights. -

Design Phase Changes

I once combined power islands. Saved 2 layers in routing stage.

Client project needed impedance control. The standard stackup met requirements. Avoid high-speed material upgrades unless necessary. I skipped additional signal tests and saved weeks. Negotiate with manufacturers regarding surface finish. Lead-free HASL costs half of ENIG.

Conclusion

Mastering 8-layer PCB stackup requires understanding configurations, accurate calculations, and cost efficiency. Apply these rules for reliable, affordable boards. Start implementing today.

[^1]: Explore this resource to understand the best practices for designing an effective 8-layer PCB stackup, ensuring optimal performance and reliability.

[^2]: Discover proven techniques for EMI control in PCB design to improve your project's performance and reduce interference issues.

[^3]: Learn effective strategies to minimize crosstalk in your PCB designs, enhancing signal integrity and overall performance.

[^4]: Understanding Dk is crucial for accurate impedance calculations in PCB design, ensuring signal integrity and performance.

[^5]: Saturn PCB Toolkit is a valuable free resource for precise impedance calculations, essential for successful PCB design.

[^6]: Cross-talk calculations are vital for maintaining signal integrity in multi-layer PCBs, preventing interference between traces.