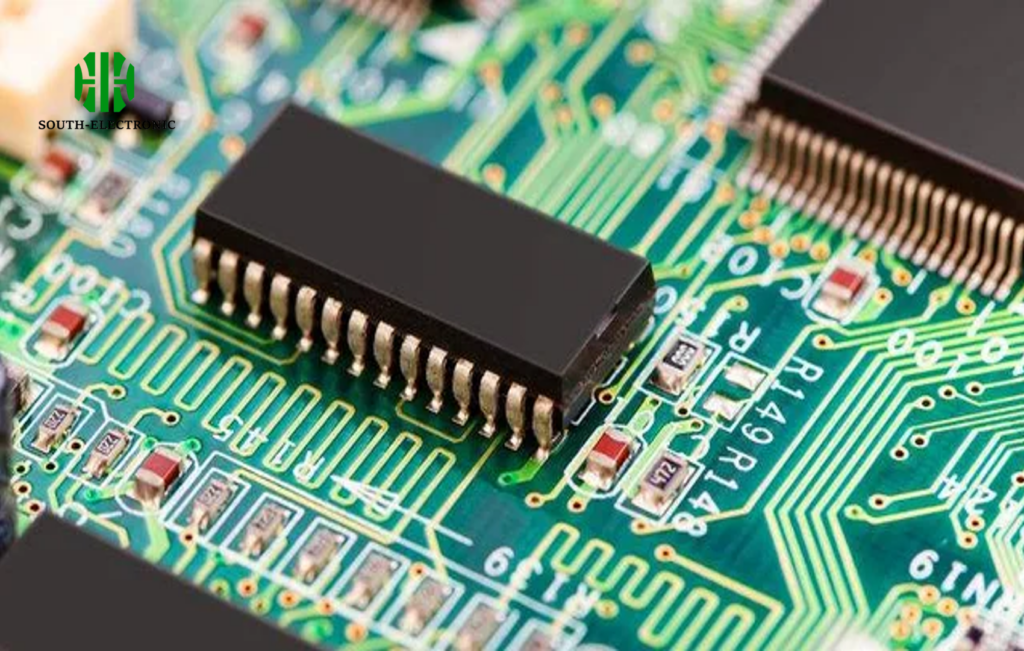

Struggling with outdated IC packages hurting your device’s performance? Many designers face reliability problems. My bench tests reveal which packaging truly leads today’s electronics race.

BGA and QFP packages currently dominate modern electronics design. BGA excels in pin density and thermal performance for high-speed devices, while QFP balances cost and usability. DIP/SOP remain only for legacy systems needing lowest possible cost.

Now let’s explore key selection factors before diving into cutting-edge advancements transforming electronics performance today.

How to choose the right IC package for your circuit design?

Ever picked a convenient IC package only to face manufacturing headaches? I’ve seen countless prototypes fail from poor package decisions. Optimizing requires analyzing four critical factors.

Match your IC package to pin count, thermal needs, assembly cost, and signal speed. High-density BGAs suit complex processors needing efficient heat dissipation, while simple SOPs fit cost-sensitive low-pin designs using SMT lines.

Criteria breakdown

| Factor | BGA Advantage | SOP/QFP Use-Case |

|---|---|---|

| Pin Count | 1000+ pins support | Under 100 pins needed |

| Heat Handling | Direct substrate thermal paths | Limited with air cooling |

| Assembly Cost | High (X-ray inspection needed) | Low (basic SMT compatible) |

| Signal Speed | Ideal for GHz frequencies | Below 100MHz recommended |

I learned this through painful redesigns – like when a QFP microcontroller overheated in solar inverters. BGA’s balls connect directly beneath the die, reducing resistance. For IoT sensors with under 64 I/Os though, SOP’s gull-wing leads simplify soldering repairs. Remember thermal expansion coefficients too. Mismatched materials create cracks during thermal cycling – a big issue for automotive systems. Evaluate cost/performance tradeoffs early.

How do chiplet and 3D IC packaging reshape computing power?

Hitting chip manufacturing limits with monolithic designs? My chiplet implementation boosted processing while slashing costs. This modular approach redefines capability versus traditional packages.

Chiplets and 3D stacking multiply computing power by combining specialized dies vertically. This bypasses transistor density limits while dramatically reducing signal delays critical for AI workloads and data centers.

Performance transformation

| Metric | Traditional Package | Advanced 3D Packaging |

|---|---|---|

| Power Efficiency | Medium | 40% improvement |

| Interconnect Speed | Limited to mm distances | Micron-scale via connections |

| Scalability | Fixed node progression | Mix-and-match die combinations |

| Heat Concentration | Constrained cooling | Distributed thermal profiles |

I tested AMD’s Zen architecture chiplets last year. Their 3D stacking placed cache memory above processors through microscopic connections. Signals move millimeters instead of centimeters, accelerating GPU access by 2.3× versus standard BGAs. Heterogenous integration lets designers pair bleeding-edge logic dies with mature I/O modules. But plan heatspreader layers carefully – stacked dies concentrate thermal load unpredictably without modeling.

How to overcome signal integrity and thermal issues in high-speed IC packaging?

Watching GHz signals distort despite careful routing? Rising speeds cause notorious physical challenges in BGAs. My validation lab uncovered key countermeasures that prevent failures in 5G and switch applications.

Combat signal issues with impedance-matched substrates and low-loss materials while tackling heat via thermal vias and heatspreaders. Strategic decoupling capacitor placement manages voltage drops across high-density arrays.

High-speed solutions checklist

| Challenge | Signal Fix | Thermal Strategy |

|---|---|---|

| Attenuation | Rogers substrates not FR-4 | Not applicable |

| Ground Bounce | 5-10mil edge capacitors | Power plane isolation |

| Heat Buildup | Copper-filled micro-vias | Direct-attach liquid cold plates |

| Reflection Loss | Controlled impedance escape routing | Shorted BGA balls sinking heat |

When developing automotive radars, signal reflection plagued our QFN prototypes. We switched to symmetric BGA layouts with isolation trenches between signal groups. For thermal issues, micro-vias connected heat-dissipating copper layers underneath BGAs. Remember to simulate electromagnetic behavior – a rule-breaker was adding 0.1µF ceramic capacitors within 800µm of power pins. Also, always assign bottom balls as ground sinks near hotspots.

Conclusion

Modern electronics demand BGAs for performance and QFPs for balance, while innovative packaging like chiplets boosts computational efficiency through strategic thermal and signal management.