Los smartphones modernos incorporan la potencia de una supercomputadora en dispositivos de bolsillo. Pero comprimir circuitos complejos en estructuras cada vez más pequeñas genera grandes dolores de cabeza en el diseño. El secreto reside en equilibrar una miniaturización agresiva con un rendimiento eléctrico impecable. Desmitifiquemos cómo se logra.

Un diseño eficiente de PCB para móviles[^1] requiere estrategias estratificadas: algoritmos de colocación de componentes, protección de la integridad de la señal, planificación de la difusión térmica y protocolos de prueba de grado militar. Priorice la optimización del espacio[^2] sin comprometer la fiabilidad: cada 0,1 mm cuenta al combatir la física en una guerra en miniatura.

Crear una PCB para smartphone no se trata solo de conexiones, sino de sobrevivir contra el calor, las interferencias y los errores humanos. A continuación, analizamos cuatro tácticas de eficacia comprobada que diferencian los prototipos funcionales de las placas listas para producción en masa.

¿Cuáles son los factores críticos para la optimización eficiente del espacio de las PCB en smartphones?

Las PCB de los smartphones deben albergar más de 1000 componentes en espacios más pequeños que las tarjetas de crédito. Una planificación deficiente provoca diafonía de señales, sobrecalentamiento o fallos de diseño irreparables.

Domine el apilamiento de componentes 3D](https://www.ipc.org/system/files/technical_resource/E17%26S01-1.pdf)[^3] utilizando placas híbridas rígido-flexibles, microvías perforadas con láser y configuraciones de chips hexagonales. Asigne entre un 15 % y un 20 % de espacio libre para zonas de disipación de calor y futuras revisiones: las placas con exceso de espacio fallan más rápido.

Análisis de la optimización del espacio

| Estrategia | Herramientas/Técnicas | Impacto |

|---|---|---|

| Gestión de capas | Placas HDI de 8 a 12 capas | Aumento de densidad del 40 % frente a 6 capas |

| Ubicación de componentes | Enrutamiento automático + ajustes manuales | Reduce la longitud de las pistas en un 22 % |

| Integración flexible | Sustratos de poliimida en zonas de flexión | Resiste más de 200 000 ciclos de plegado |

| A prueba de futuro | Reserva áreas para latas de blindaje de RF | Permite cambios de antena de última hora |

Comience con la planificación del apilamiento de capas: combine estratégicamente las capas de señal, tierra y potencia. En una ocasión, ahorré 2,3 mm² al reemplazar matrices de chips circulares por hexagonales. Utilice microvías escalonadas (0,1 mm de diámetro) en lugar de orificios pasantes para las conexiones verticales. Siempre verifique los resultados del enrutamiento automático; las máquinas no pueden predecir el acoplamiento capacitivo inducido por los dedos cerca de las pantallas táctiles.

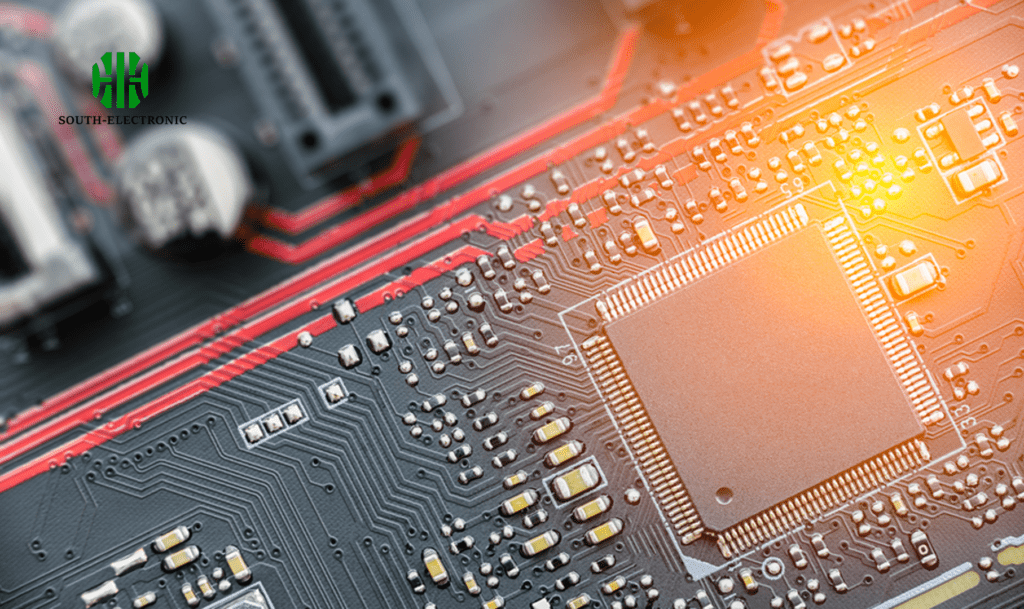

¿Cómo garantizar la integridad de la señal en circuitos móviles de alta velocidad?

Los teléfonos inteligentes combinan simultáneamente señales 5G, WiFi 6E y UWB. La interferencia electromagnética (EMI) sin control convierte los dispositivos en inhibidores portátiles.

Implemente enrutamiento diferencial de pares[^4] para buses de velocidad GHz, aislamiento de vertido de tierra entre módulos de RF y almohadillas definidas por máscara de soldadura. Realice pruebas TDR para verificar las coincidencias de impedancia[^5]—las discrepancias superiores a 5 Ω causan reflexiones de señal.

Medidas de seguridad para la integridad de la señal

| Factor de riesgo | Solución | Mejora del rendimiento |

|---|---|---|

| Diafonía | Regla de 3 W (espaciado de trazas ≥ 3 veces el ancho) | Reducción de ruido de 18 dB |

| Deriva de impedancia | Constantes dieléctricas simuladas | Control de impedancia de ±2 % |

| Rebote de tierra | Planos de potencia divididos + desacoplamiento | Rizado de VCC 30 % menor |

| Acoplamiento de antena | Carcasas de blindaje de jaula de Faraday | Aislamiento de 55 dB entre radios |

Enrute primero las líneas de memoria DDR4/5; sus tolerancias de sincronización son las más ajustadas. He solucionado el parpadeo de la pantalla añadiendo protectores de tierra cerca de las líneas MIPI DSI. Para antenas de ondas milimétricas (28 GHz o más), utilice sustratos Rogers 4350B en lugar del FR4 estándar para minimizar la pérdida. Siempre termine las líneas de reloj con resistencias adaptadas a la impedancia característica.

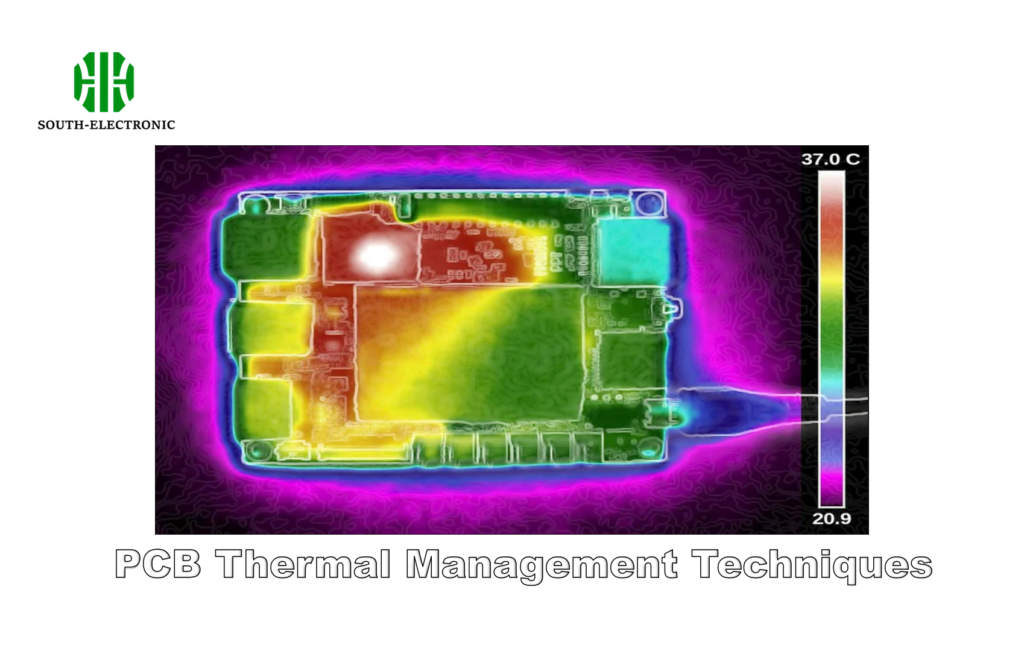

¿Por qué la gestión térmica es fundamental para la longevidad de las PCB móviles?

El SOC de un smartphone puede alcanzar los 110 °C durante los juegos, suficiente para fundir las soldaduras. Sin disipación de calor, su teléfono de 1000 $ se convierte en un pisapapeles en 6 meses.

Implemente vías térmicas rellenas de cobre debajo de chips calientes, disipadores de calor de grafito y almohadillas térmicas de cambio de fase. Mantenga las uniones de los componentes por debajo de 85 °C: cada disminución de 10 °C duplica su vida útil.

Comparación de Técnicas de Refrigeración

| Método | Ideal para | Resistencia Térmica (°C/W) |

|---|---|---|

| Matriz de Vías Térmicas | Puntos calientes de CPU/GPU | 15-20 |

| Láminas de Disipación de Calor | Áreas de Batería/PMIC | 25-30 |

| Polímero de Cristal Líquido | Módulos Front-End de RF | Más de 40 |

| Aislamiento de Espacio de Aire | Sensores de Cámara | Más de 50 |

Coloque los sensores de temperatura cerca de los PMIC y los circuitos integrados de carga; son puntos calientes de fallo. Durante un proyecto con una tableta, el uso de 576 vías térmicas bajo el SOC redujo las temperaturas máximas en 14 °C. Evite usar blindajes metálicos sobre los módulos WiFi/BT, ya que retienen el calor. En su lugar, utilice blindajes de polímero con microorificios de ventilación.

¿Qué métodos de prueba garantizan la robusta funcionalidad de las PCB móviles?

El 60 % de las fallas en campo se deben a defectos de diseño no detectados. Las pruebas exhaustivas detectan defectos en la máquina antes de la producción en masa.

Combine la inspección óptica automatizada (IOA) (https://zh.wikipedia.org/zh-tw/%E8%87%AA%E5%8B%95%E5%85%89%E5%AD%B8%E6%AA%A2%E6%9F%A5)[^6], las pruebas de sonda volante y el ciclo de choque térmico (https://www.ipc.org/system/files/technical_resource/E16%26S36-03.pdf)[^7]. Para placas de misión crítica, utilice el SYSCAN JFU-5200 para escaneos de límites JTAG de 360°: detecta el 99,97 % de los defectos latentes.

Desglose del protocolo de prueba

| Etapa de prueba | Equipo utilizado | Comprobaciones realizadas | |

|---|---|---|---|

| Premontaje | Inspección por rayos X | Integridad de las microvías | |

| Post-SMT | Máquinas AOI 3D | Volumen de pasta de soldadura | |

| Pruebas funcionales | Analizadores de carga de CC | Estabilidad del riel de alimentación | |

| Ambiental | Cámara de choque térmico | Resistencia al ciclo de -40 °C a 125 °C | |

| Simulación de campo | Probadores de caída (1,5 m de altura) | Durabilidad de la unión BGA | Durante las pruebas del módulo de audio, descubrí un zumbido en la bobina solo al sondear a un ancho de banda de 200 MHz. Pruebe siempre los circuitos de carga con cables no compatibles; los usuarios lo harán. Para teléfonos resistentes al agua, realice pruebas de contaminación iónica después del recubrimiento conformado. Dedique el 14 % del tiempo del proyecto a la validación del diseño; esto evita el 90 % de los riesgos de retirada del mercado. |

Conclusión

Dominar el diseño de PCB para móviles exige precisión: optimice los espacios como Tetris, proteja las señales como Faraday, enfríe los componentes como refrigeradores y realice pruebas como científicos paranoicos. Prepare sus placas para el futuro, porque la tecnología del mañana cabe en el espacio de ayer.

[^1]: Explore este recurso para comprender las últimas técnicas y estrategias para optimizar el diseño de PCB en smartphones, garantizando la fiabilidad y el rendimiento.

[^2]: Descubra estrategias eficaces para la optimización del espacio en PCB de smartphones para evitar fallos de diseño y mejorar el rendimiento en diseños compactos.

[^3]: Conozca las ventajas del apilamiento de componentes 3D en el diseño de PCB, que puede mejorar significativamente la eficiencia del espacio y la gestión térmica. [^4]: Comprender el enrutamiento de pares diferenciales puede mejorar significativamente el diseño de su circuito, garantizando una mejor integridad de la señal y un mejor rendimiento.

[^5]: Aprender sobre la adaptación de impedancia es crucial para optimizar la integridad de la señal y minimizar las reflexiones en sus diseños.

[^6]: Explore este enlace para comprender cómo AOI mejora la eficiencia y la precisión de las pruebas de PCB, garantizando una producción de alta calidad.

[^7]: Aprenda sobre los ciclos de choque térmico para ver cómo prueba la durabilidad de la PCB en condiciones extremas, crucial para un rendimiento confiable.