Вы когда-нибудь тратили недели на отладку печатной платы только для того, чтобы найти неправильное соединение? Список соединений печатной платы предотвращает этот кошмар, выступая в качестве ДНК схемы. Позвольте мне объяснить, почему этот скромный текстовый файл является основой вашего проекта.

Список соединений печатной платы — это текстовый файл ASCII, определяющий электрические соединения между выводами компонентов. Он соединяет схемы и физическую компоновку, позволяя проводить моделирование и автоматическую проверку ошибок, что делает его единственным источником истины для функциональности печатной платы.

Хотя понимание списков соединений кажется техническим, освоение их роли может предотвратить катастрофические ошибки проектирования. Давайте разберем, как они работают в разных системах и на разных этапах.

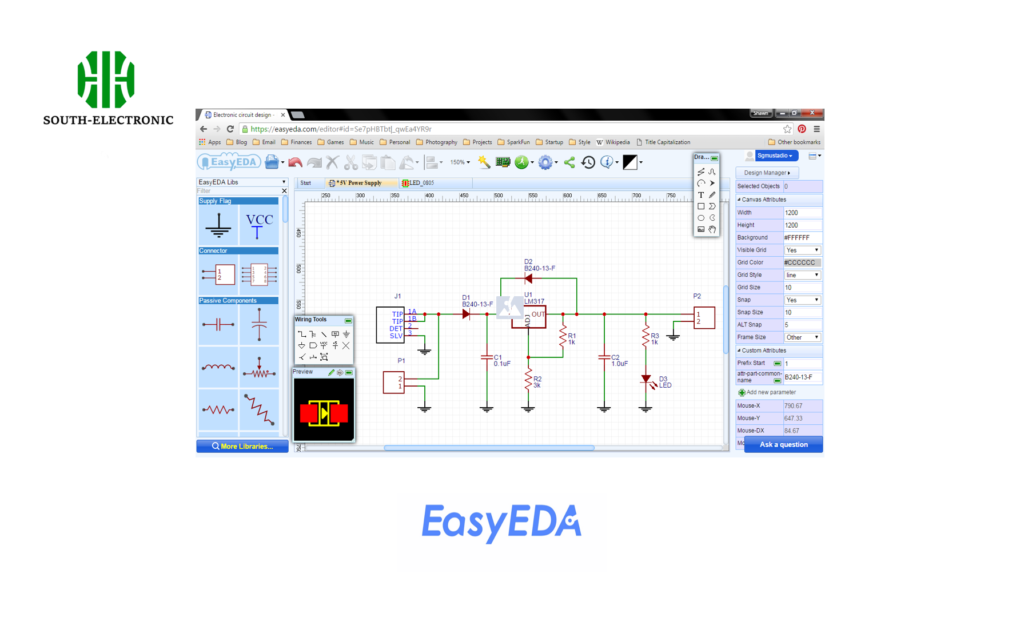

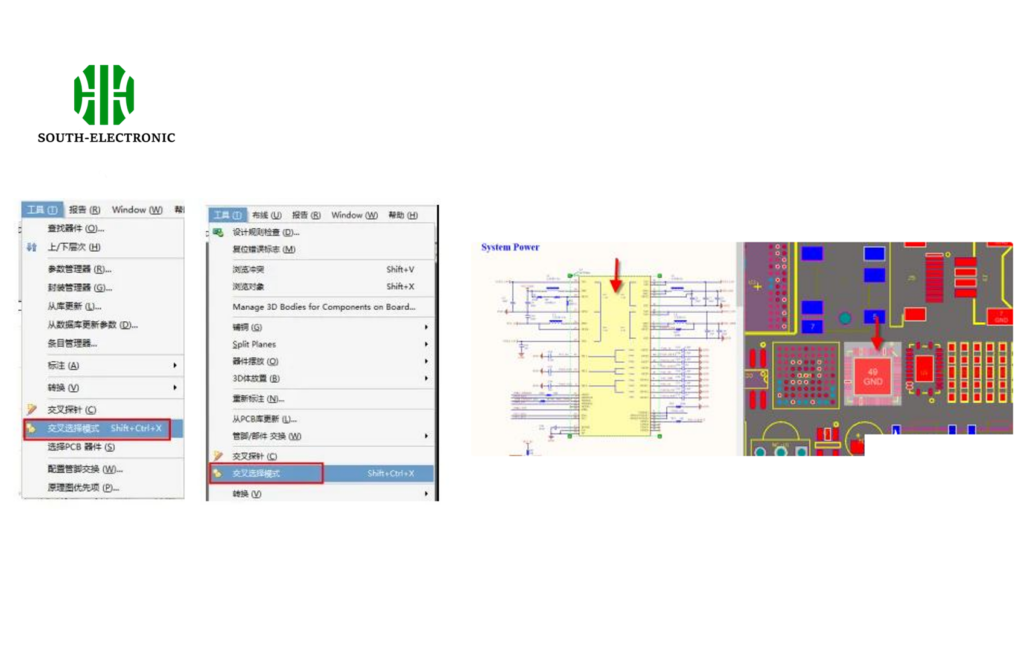

Как инструменты EDA генерируют список соединений?

Посмотрите, как ваша схема преобразуется в машиночитаемые инструкции. Инструменты EDA генерируют списки соединений, интерпретируя ваши чертежи как математические соединения, но не все инструменты делают это одинаково.

Программное обеспечение EDA, такое как Altium Designer, создает списки соединений, анализируя выводы и провода компонентов в схемах. Современные инструменты добавляют метаданные, такие как классы цепей и дифференциальные пары, для руководства по компоновке.

Процесс генерации списка цепей

Большинство инструментов выполняют три шага:

| Шаг | Действие | Критические контрольные точки |

|---|---|---|

| 1. Анализ схемы | Считывает символы компонентов и соединения проводов | Проверяет, соответствуют ли количества выводов символов посадочным местам |

| 2. Проверка электрических правил | Проверяет наличие коротких замыканий/разомкнутых цепей | Отмечает неподключенные выводы питания |

| 3. Экспорт формата | Сохраняет в формате SPICE/EDIF/других форматах | Подтверждает совместимость с целевым инструментом компоновки |

Главное — согласованность. В прошлом месяце печатная плата моего коллеги вышла из строя, потому что его инструмент EDA использовал строчные буквы «gnd», тогда как в макете ожидалось «GND». Всегда проверяйте заглавные буквы в имени сети на ранней стадии.

Почему проверка списка соединений критически важна перед компоновкой печатной платы?

Пропуск проверок списка соединений похож на сборку без чертежей. Согласно исследованиям IEEE, 63% ошибок после компоновки связаны с непроверенными списками соединений.

Проверка списка соединений сравнивает схемные соединения с созданным файлом и целевыми правилами. Она выявляет несоответствия, такие как переставленные контакты или отсутствующие компоненты, до дорогостоящего производства.

Общие области проверки

Создайте контрольный список, соответствующий этим приоритетам:

| Тип проверки | Используемые инструменты | Обнаруженные критические ошибки |

|---|---|---|

| Электрические | SPICE, HyperLynx | Короткие замыкания, плавающие узлы |

| Логические | FormalCheck, пользовательские скрипты | Несоответствия направления сигнала |

| Физические | Сравнение CAD, DIFF | Несоответствия количества выводов посадочного места |

Однажды я видел прототип стоимостью 25 тыс. долларов, потому что линия данных DDR4 была подключена к неправильному банку — это было мгновенно обнаружено при проверке списка соединений, но невидимо в схемах. Проверьте трижды, прототипируйте один раз.

Список соединений SPICE против EDIF: какой формат подходит вашему проекту?

Выбрать неправильный формат — это как говорить по-французски в Токио. Списки соединений SPICE и EDIF служат разным хозяевам — знайте, какой из них понимают ваши инструменты.

Используйте списки соединений SPICE (.cir) для моделирования цепей и аналогового анализа. Выберите EDIF (.edf) для компоновки печатной платы и интеграции цифровых систем.

Руководство по сравнению форматов

| Фактор | SPICE | EDIF |

|---|---|---|

| Лучше всего подходит для | Моделирования | Многоинструментальной совместной работы |

| Типы данных | Аналоговые параметры | Иерархические данные проектирования |

| Поддержка инструментов | LTspice, PSpice | Cadence Allegro, Altium |

| Читаемость | Удобочитаемость для человека | Оптимизация для машины |

При проектировании платы IoT со смешанными сигналами в прошлом году я использовал SPICE для проверки датчиков и EDIF для компоновки, что доказывает необходимость гибридов в обоих форматах. Подберите формат к текущей фазе.

7 ошибок в списке соединений, которые могут испортить ваш прототип печатной платы

Вы когда-нибудь видели, как опечатка за 10 долларов убивает плату за 10 тысяч долларов? Эти тихие убийцы списка соединений ускользают от базовых проверок.

К основным фатальным ошибкам списка соединений относятся переставленные дифференциальные пары, дублирующиеся имена цепей, отсутствующие цепи питания, неправильное сопоставление выводов, неподключенные разрешения микросхем, несоответствия символов и посадочных мест и неэкранированные специальные символы.

Контрольный список по предотвращению ошибок

| Тип ошибки | Метод обнаружения | Совет по предотвращению |

|---|---|---|

| Перестановка выводов | Сравнение с техническими паспортами | Выделение критических сетей в схемах |

| Отсутствующие сети | Инструменты перекрестного зондирования | Используйте ERC со строгими правилами |

| Конфликты имен | Уникальная маркировка сетей | Примите именование "_" |

Отсутствующее подчеркивание в "3V3_Audio" против "3V3Audio" однажды объединило шины питания, поджарив операционные усилители. Никогда не недооценивайте соглашения об именовании.

Заключение

Списки соединений печатных плат преобразуют абстрактные схемы в готовые чертежи. Выбирая правильные форматы, проводя тщательные проверки и охотясь на скрытые ошибки, вы превратите этот технический шаг в свое секретное оружие надежности.