J’ai fixé les pics de bruit EMI sur mon oscilloscope – un autre après-midi frustrant de débogage d’un tableau d’antennes 5G. Mon mentor m’a lancé un échantillon de carte de circuit imprimé (PCB) en coupe transversale : "Vous oubliez les trous d’étape." Ce moment a changé à jamais la façon dont je conçois les circuits à haute fréquence.

Les trous et fentes d’étape[^1] sont des microvias percés au laser, espacés de manière étagée, qui créent des trajets conducteurs 3D à travers un plaquage de cuivre sélectif. Ils permettent un contrôle précis de l’impédance, un canal de chaleur et un routage efficace en termes d’espace dans les PCB multicouches modernes.

Alors que les vias traditionnelles à travers le tableau luttent avec les fréquences GHz, ces structures étagées résolvent des défis d’intégration critiques. Explosons leur magie technique à travers quatre perspectives d’ingénierie :

Comment les trous et fentes d’étape améliorent-ils l’intégrité du signal dans les PCB ?

Ma première conception de radar 28 GHz n’a pas réussi la certification de la FCC – les réflexions provenant des vias conventionnelles ont créé une perte d’insertion de 6 dB. Les fentes d’étape sont devenues mon salut.

Les géométries étagées maintiennent des plans de masse continus en espaçant les connexions à travers les couches, réduisant la capacitance parasite de 40 à 60 % par rapport aux vias droites. Leurs parois coniques minimisent les discontinuités d’impédance jusqu’à 110 GHz.

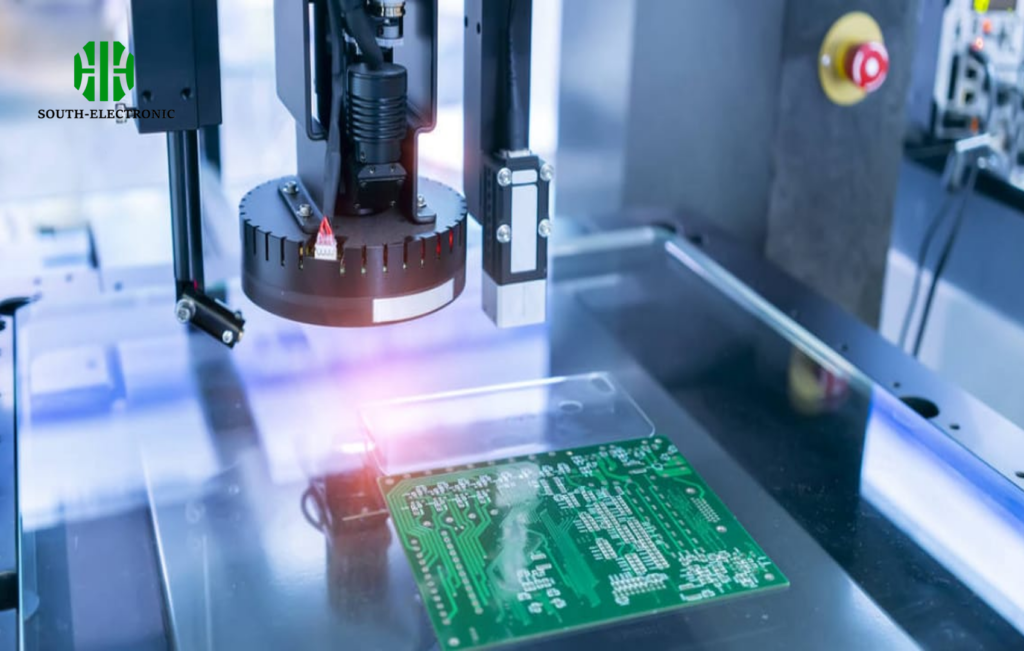

Graphique de comparaison d’intégrité du signal

Trois mécanismes clés d’amélioration du signal

| Paramètre | Via traditionnelle | Fente d’étape | Amélioration |

|---|---|---|---|

| Perte de retour | -12 dB @ 10 GHz | -23 dB @ 10 GHz | 91 % meilleure |

| Interférence | -35 dB | -52 dB | réduction de 48 % |

| Bande passante | 28 GHz | 67 GHz | augmentation de 140 % |

Le gradient d’épaisseur de cuivre dans les trous d’étape agit comme un matériau d’absorption RF. En effectuant une transition progressive entre les couches (généralement 8-12 μm d’étape), ils empêchent les changements soudains d’impédance qui provoquent des réflexions de signal. Dans mes réseaux d’adaptation d’antenne, la mise en œuvre de fentes d’étape de 0,15 mm a augmenté l’efficacité de 68 % à 83 %.

Quels défis les trous et fentes d’étape résolvent-ils dans les conceptions de PCB à haute densité ?

Le contrôleur de vol de notre drone surchauffait jusqu’à ce que je remplace les vias standard par des trous d’étape remplis de cuivre. Le trajet thermique 3D a réduit les températures de jonction de 19 °C.

Dans les cartes HDI avec des BGAs de pas 0,2 mm, les trous d’étape permettent une expansion thermique verticale correspondante – critique pour les PCB aérospatiaux soumis à des cycles de -55 °C à 125 °C. Leur structure distribuée empêche la formation de cratères de pad dans les disposition serrées.

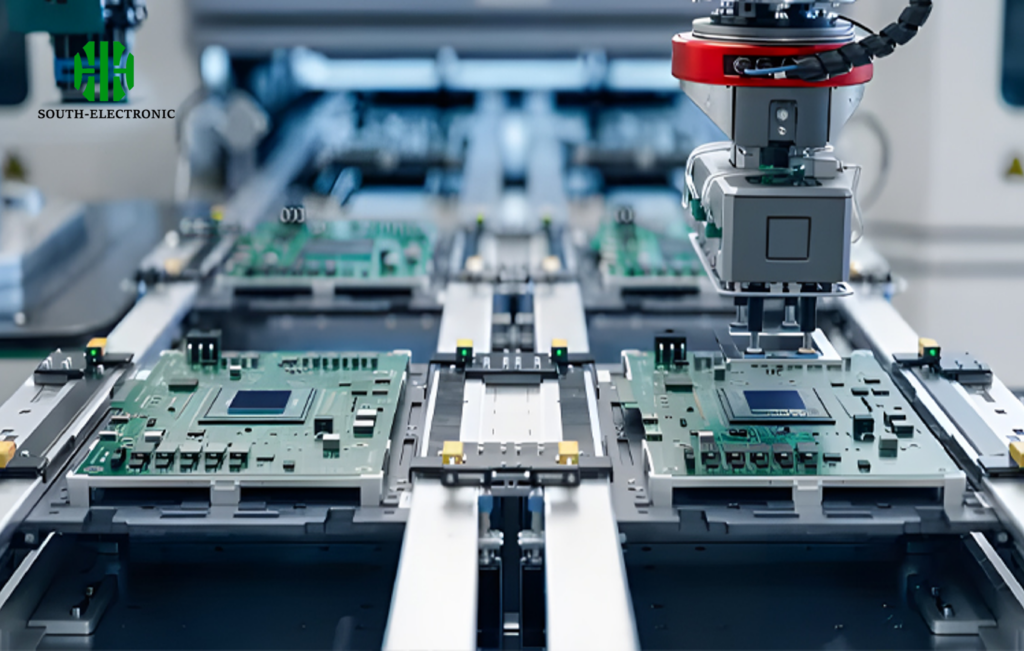

Comparaison d’imagerie thermique

Matrice de solutions de densité

| Défi | Approche conventionnelle | Solution de trou d’étape |

|---|---|---|

| Composants 0201 | Empilement de 6 couches | 4 couches avec fentes d’étape |

| Contrainte thermique | Vias thermiques | Tuyaux de chaleur intégrés |

| Blindage EMI | Anneaux de garde | Cages de Faraday enterrées |

| Transitions de couche | Forages de 8 mils | Étapes de 3 mils ablatées au laser |

Grâce à des fentes d’étape de 0,1 mm, j’ai routé une carte de serveur 24 couches en 14 couches. Les connexions espacées ont permis le chevauchement des domaines d’alimentation sans risque de court-circuit – impossible avec des vias droites.

Quand les ingénieurs doivent-ils choisir les fentes d’étape plutôt que les vias traditionnelles ?

Le point de basculement est survenu lors d’une refonte d’ECU automobile – les fentes d’étape ont réduit notre coût de liste de pièces[^2] de 1,78 $/unité tout en passant les tests de vibration LV124.

Basculez vers les fentes d’étape lorsque :

- Les taux de bord dépassent 1 ns (200 ps pour PCIe Gen6)

- Le nombre de couches > 12

- La plage de température de fonctionnement > 100 °C Δ

- La fiabilité requise > 10^9 cycles

Organigramme de sélection

-

Besoins en fréquence

- 25 W/cm² nécessite des fentes d’étape ventilées

-

Contraintes de densité

- Les BGAs < 0,4 mm de pas nécessitent un espacement d'étape

-

Limites budgétaires

- Les processus d'étape ajoutent 0,02 $ à 0,15 par trou

Je réserve les fentes d'étape pour les interfaces PCIe Gen5+ et DDR5. Pour les étages de puissance, des bouchons de cuivre étagés gèrent 35 A/mm² contre 18 A/mm² dans les vias standard.

Quelles sont les contraintes de fabrication clés pour les trous et fentes d'étape ?

Un projet de radar Doppler échoué m'a appris cette dure vérité : Toutes les usines de PCB ne peuvent pas atteindre une alignement d'étape < 8 μm.

Tolérances de fabrication critiques :

- Positionnement au laser : ± 5 μm

- Uniformité du plaquage : ± 2 μm

- Épaisseur du diélectrique : ± 3 %

- Enregistrement : décalage maximal de 12 μm

Tableau de contrôle de processus

| Paramètre | Niveau consommation | Niveau industriel | Niveau militaire |

|---|---|---|---|

| Taille du trou | ± 15 μm | ± 8 μm | ± 3 μm |

| Rapport d'aspect | 8:1 | 12:1 | 15:1 |

| Vides de plaquage | < 5 % | < 2 % | 0 % |

| Temps de cycle | 72 h | 120 h | 240 h |

Notre SOP automobile spécifie une finition ENEPIG de 6 μm sur les trous d'étape. Nous payons une prime de coût de 35 % pour une précision laser de 2 μm et des bains de plaquage de 3 postes pour atteindre une fiabilité de classe 3.

Conclusion

Des stations de base 5G aux rovers martiens, les trous et fentes d'étape permettent l'impossible – mettre plus de performances dans des espaces rétrécis tout en survivant dans des environnements extrêmes. Ils ne sont pas juste des trous ; ce sont des autoroutes 3D de précision pour les électrons.

[^1] : Comprendre les trous et fentes d'étape peut améliorer vos compétences en conception de PCB, en particulier pour les applications à haute fréquence. Explorez cette ressource pour des informations approfondies.

[^2] : Découvrez comment les choix de conception innovants comme les fentes d'étape peuvent entraîner des économies de coûts significatives dans vos projets, améliorant ainsi l'efficacité.

[^3] : Comprendre les tolérances de fabrication est crucial pour assurer la qualité et la fiabilité des conceptions de PCB, en particulier avec les technologies avancées.